( ESNUG 596 Item 7 ) ----------------------------------------------------- [04/12/2024]

Subject: hands-on user benchmark confirms SNPS ASO.ai gets 50% analog migration done

Beckley: That's in combination with a lot of work we did with TSMC to enable

that node-to-node migration. It's not easy, but it's both schematic

and it's layout as well.

So, it does work, John. Does my Studio do everything completely? No.

Does my Virtuoso Studio do maybe 80 percent of it? Yes.

And that's huge.

- DAC'23 Troublemaker Panel: Beckley claims Virtuoso does 80% analog migration

---- ---- ---- ---- ---- ---- ---- ---- ----

EDITOR'S NOTE: So my personal Cooley 3 part mission while at SNUG was as follows:

- Find an ASO.ai user benchmark at SNUG'24

- Assess exactly who is giving this ASO.ai benchmark

- Then, if they're worthwhile, actually review their ASO.ai benchmark

Since I found an ASO.ai benchmark at SNUG, here's my assessing who gave it... - John

---- ---- ---- ---- ---- ---- ---- ---- ----

YVONNE HAS STREET CRED: Whenever I review any new tool benchmark, I ask a few common

sense questions to ascertain how credible to take this particular benchmark. Since

this is the first Artificial Intelligence custom design tool benchmark anywhere -- and

since it's in a niche where a big Shankar-vs.-Beckley battle is unfolding, I'm

especially concerned about exactly who is doing this first AI custom tool benchmark.

Q: Is this Yvonne a SNPS employee shilling for ASO.ai?

A: Nope. Yvonne (Ya-Fen) Lin works at Credo -- and not at SNPS.

Q: Is this Yvonne personally qualified to do an analog migration benchmark?

A: Yes. Yvonne has:

10 years at TSMC hands-on using CDNS Virtuoso on FLASH and FinFET designs

2 years at Inphi hands-on using SNPS Custom Compiler and CDNS Virtuoso

3 years at Credo hands-on using SNPS Custom Compiler

That is, in my book Yvonne has the hands-on street cred to do this benchmark.

Q: Is Yvonne telling the whole story (good and bad) about using ASO.ai?

A: I give a VERY LOUD "Yes!" to that -- but see for yourself here below ...

---- ---- ---- ---- ---- ---- ---- ---- ----

"Why we're migrating our analog TSMC N5 design over to TSMC N7..."

WHAT COOLEY HEARD: "blah blah blah we had to migrate our working 5nm VCO PLL analog

design over to 7nm because TSMC has open 7nm fab capacity available ... while we'd

have to wait for God-Knows-how-long for a slot in TSMC's 5nm fab to open... blah

blah blah also 5nm would cost more ... plus TSMC 7nm has great yields now..."

"... blah blah since our 5nm VCO PLL was orginally designed using Custom Compiler and

we got good results with CC, we figured we'd try out the new ASO.ai that rides on

top of Custom Compiler ... blah blah our SNPS FAEs said other users were getting

good results with ASO.ai driving Custom Compiler ... blah blah so why not try it?"

---- ---- ---- ---- ---- ---- ---- ---- ----

COOLEY HEARD: "Our small 5nm VCO PLL is the best way to test out this ASO.ai stuff."

---- ---- ---- ---- ---- ---- ---- ---- ----

COOLEY NOTE: Notice all the yellow "manual" in her flow chart above? That's why she

was trying out ASO.ai -- to get all those manual steps to become automatic.

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

BACKGROUND: All present day SNPS analog migrations have the same 7 basic steps:

A. Input Sources source schematic, testbenches, specifications, and layout

B. Create Remap Library create a source-cell-to-target-cell remapping library

C. Migrate Schematics remap all source cells to target cells

D. Recenter Design 1st run to tweak devices in target design

E. Generate Layout create 1st layout of recentered target design

F. Optimize Design iterate between parasitics and layout ECOs in target design

G. Finishing do target finishing and target signoff

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

"Step B: Create Remap Library"

COOLEY NOTE: Here's where Yvonne created the remapping library with ASO.ai driving

Custom Compiler. First, she's setting up the N5 to N7 mapping table. Each source

TSMC N5 cell is remapped to an equivalent target TSMC N7 cell.

In ASO.ai, she does the usual substeps of

1. library selections plus PDKs

2. configuring the reference libs

3. specifying parameter mapping with conditions

but what caught my eye was details of cell mapping with conditions could be:

---- ---- ---- ---- ---- ---- ---- ---- ----

Then -- POOF! -- a new TSMC N5-to-N7 mapping library is created in minutes.

---- ---- ---- ---- ---- ---- ---- ---- ----

"Step C: Migrate Schematics

COOLEY NOTE: with this new N5-to-N7 mapping lib, now the actual schematic generation

happens. That is, it's the actual schematic migration itself. Every source N5

cell is brute force replaced with it's equivalent target N7 cell.

---- ---- ---- ---- ---- ---- ---- ---- ----

"Step D: Recenter Design (part 1)

COOLEY NOTE: what's interesting is there's an awful lot of "transistor tweaking"

(over ~13,000 combinations) to meet all the corners and all the possible parameter

(transistor) dimensions of her 7nm target design.

---- ---- ---- ---- ---- ---- ---- ---- ----

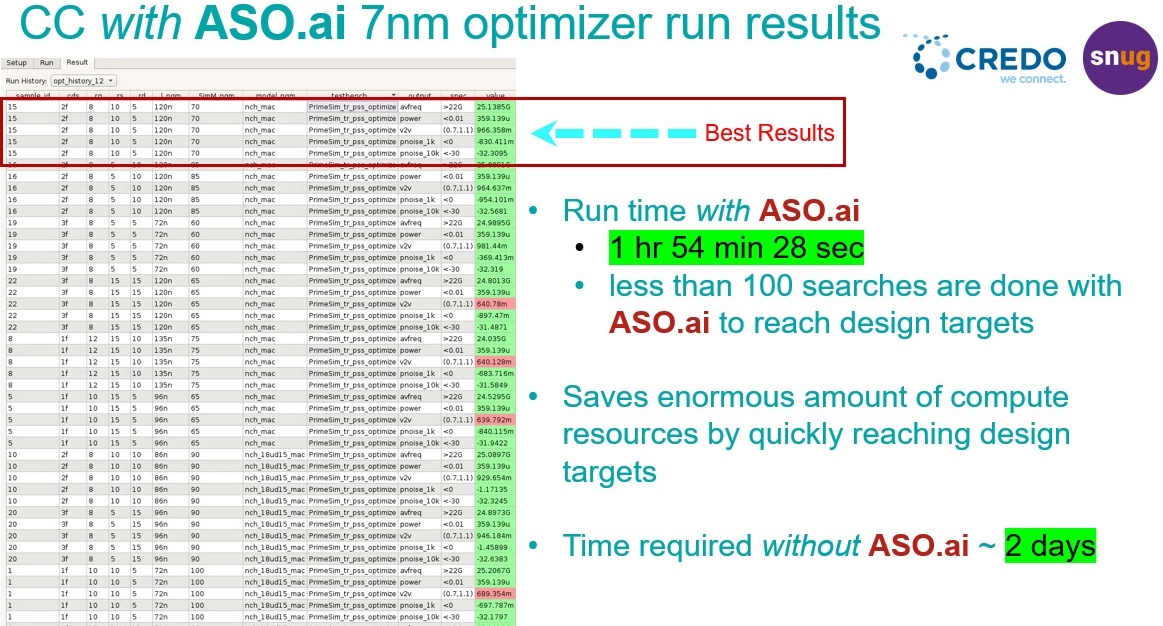

"Step D: Recenter Design (part 2)

(click on pic to enlarge image)

|

COOLEY NOTE: Instead of running all 13,000 possible combinations, ASO.ai does some

clever reinforcement learning that instead converges to the spec in 100 iterations.

For example, the Credo specs for their 7nm target design are:

Average Frequency: greater than 22 GHz

Power: less than 10 mW

Voltage Swing: 0.7 Volts

Phase Noise at 1k offset: less than 0 dBc/Hz

Phase Noise at 10k offset: less than -30 dBc/Hz

To put this in perspective, the Credo guys say that one of their veteran analog

designers could do this by hand with Custom Compiler in roughly 2 days. ASO.ai

did it in 2 hours -- a 24 to 1 speed-up.

---- ---- ---- ---- ---- ---- ---- ---- ----

WHY HALF BENCHMARK? The happy faces and big "NOT" symbols in the SNPS analog migration

flow chart below are my quick Cooley Report Card of how this ASO.ai benchmark went:

100% A. Input Sources source schematic, testbenches, specifications, and layout

100% B. Create Remap Library create a source-cell-to-target-cell remapping library

100% C. Migrate Schematics remap all source cells to target cells

100% D. Recenter Design 1st run to tweak devices in target design

0% E. Generate Layout create 1st layout of recentered target design

50% F. Optimize Design iterate between parasitics and layout ECOs in target design

0% G. Finishing do target finishing and target signoff

COOLEY NOTE: Basically the Credo engineer, Yvonne, did all the stages (Steps A to D)

all the way up to (but having to stop at) anything layout -- meaning NO Step E and

only the top part of Step F. That is, Yvonne couldn't perform the layout/parasitics

iterations in Step F because she had no 7nm layouts to iterate with!

Here's how Yvonne herself showed what her ASO.ai benchmark did (and didn't) accomplish:

Notice the light blue parts are what Yvonne did. And the Synopsys purple parts are

what's coming in the future -- namely all the automated layout parts are coming.

WHY COOLEY LIKES THIS BENCHMARK: Instead of focusing on what this Credo benchmark didn't

do, let's look at what it did do.

- it showed that Automated Schematic Migration works in ASO.ai.

- more importantly, it showed ASO.ai did Automated AI-based Circuit Optimation

that took 13,000 possible combinations -- and used AI-magic to boil it down

to 100 iterations that covered all the corners -- and met spec in 2 hours!

That "Automated AI-based Circuit Optimation in 2 hours" news is what makes this

particular ASO.ai user benchmark worth citing.

---- ---- ---- ---- ---- ---- ---- ---- ----

FOOTNOTE (for completeness)

SIGNS OF A GOOD BENCHMARK: While pointing out the specific 5nm to 7nm remapping issues

she solved in ASO.ai, Yvonne again also reminded us of what ASO.ai didn't do (because

it lacked all layouts) in her benchmark, namely:

- resolve the MINCAP difference between TSMC 5nm and 7nm

- resolve the 5nm CNOD to 7nm PODE issues

- resolve the 5nm VG is not available in 7nm issue

And in her other slides, Yvonne pointed out how in "Step F: Optimize Design" ASO.ai

still needs to do Monte Carlo and PVT corner reduction optimizations there, too.

It's her attention to detail plus her brutal honesty that -- by her actions -- tells

me this 30 slide user benchmark is worth publically citing.

I tip my hat to you, Yvonne. Job well done.

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

HOLY CRAP! SHANKAR THROWS THE FIRST PUNCH!: In my universe there's a massive difference

between what an EDA vendor claims his tool can do (aka Beckley's Virtuoso Studio at the

DAC'23 Troublemakers Panel last year) vs. what the actual hands-on users actually

confirm what an EDA vendor's tool can do (aka Shankar's ASO.ai user here at SNUG'24.)

So I have to -- for now -- give my congrats to Shankar for throwing the first real punch in

this new winner-takes-a-big-chunk-of-custom-design-$$$$ analog migration war.

- John Cooley of DeepChip.com (04/11/2024)

---- ---- ---- ---- ---- ---- ---- ---- ----

Related Articles

Whoa - Sassine's first real speech anywhere was his keynote at SNUG'24

WTF? - Sassine held his very first SNPS Investor Day at SNUG'24???

WTF? - Scooby Doo Mystery; why did Ravi launch a mediocre ZeBu EB2 at SNUG'24?

Whoa - Shankar is now seriously gunning for Tom Beckley's Virtuoso empire

Whoa - hands-on user benchmark confirms SNPS ASO.ai gets 50% analog migration

Zing - Sassine's unfair advantage in hard design IP ... but not in soft VIP

Join

Index

Next->Item

|