( ESNUG 596 Item 1 ) ------------------------------------------------------- [03/21/24]

Subject: Beckley on how his Virtuoso Studio is 80% crushing custom process migration

The live DAC'23 Troublemakers Panel

Cooley: Tom. I know a lot of customers are using Virtuoso, but you've had

multiple launches into upgrading into different things.

Why should they want to use Virtuoso Studio?

Beckley: We've had many launches, you're right. Because technology

changes it, advances especially with advanced nodes.

And we made a big move back in the mid-2000 timeframe, when we moved

to the Open Access database for our industry, right?

That was a huge move for us, and it's actually taken us into 2nm now.

So, the reason we're moving is because our customers have new demands;

tens of thousands of corners.

We had never seen that before.

We just launched a revamped frontend and revamped simulation

environment.

We can handle tens of thousands of corners which we now see in

advanced nodes.

We can handle the capacity of advanced nodes, and we can handle

chip and package and chiplets to the heterogenous designs.

And that's why we call it Virtuoso Studio by the way -- we can

handle all the capacity requirements, and we can handle the types

of designs for a world of "more than Moore" that we're seeing now.

Of course, some parts are treated with Fast SPICE, some parts are

treated with SPICE.

All of those types of permutations and combinations -- including

doing advanced packaging -- especially if it's an RF IC or if

there's sensors involved or if there's photonics involved, then

Virtuoso Studio really is the way to go.

That's why we're doing it. And by the way, it will be where we do

all of our new AI work.

Cooley: Okay. I've got to do a follow-up because I saw this when you

launched it at Cadence Live 2023, one of the things you were talking

about is doing process migration in Virtuoso.

Beckley: Yes.

Cooley: Are you crazy?

Beckley: You should ask Sony that, you should ask Renesas that, because

they are doing it using us.

Cooley: From what node to what node?

Beckley: One is moving from planar (CMOS) to FinFET that's on the image sensor

side so you can figure out who that is.

And then the other one's moving from FinFET 7nm-to-3nm or FinFET 7nm-to-5nm.

I'm not 100 percent sure about that.

Beckley: That's in combination with a lot of work we did with TSMC to enable

that node-to-node migration. It's not easy, but it's both schematic

and it's layout as well.

So, it does work, John. Does Studio do everything completely? No.

Does Studio do maybe 80 percent of it? Yes.

And that's huge.

Cooley: Yeah. That's huge.

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

[ EDITOR'S NOTE (1): I asked the CDNS guys to back up their customer adoption

claims. This is what they sent me:

"Our Virtuoso has 1500+ customers, and we add over 15% new customers

per year. In 2022 + 2023 we added 300+ new logos."

"Our new Virtuoso Studio has had the highest number of downloads ever

for any Virtuoso release within the first 6 months after release."

"Roughly 30-40% of our installed base has switched to Virtuoso Studio;

with 18 of the 20 Top semi manufacturers using it in production and

10 of the Top 20 using it for process migration."

Here's my quick dissection of these CDNS claims:

I only found 15 (not 18) of the Top 20 for production and 8 (not 10) using

Virtuoso Studio for process migration -- and with 1 tapeout even!

Virtuoso 2016

|

|

Virtuoso 2024

|

COOLEY ANALYSIS: Not bad. It's not a repeat of their 2016 fiasco launch of

Virtuoso ADE Explorer, ADE Assembler, and ADE Verifier from 8 years ago.

(Which flopped big time with ADE users! See ESNUG 560 #1. Disaster city!)

But now 8 years later in 2024, I'm finding a good number of custom users

using (or seriously trying) Virtuoso Studio now -- especially to solve that

Big $$$$ & muy lucrative process migration problem. Congrats, Tom! - John ]

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ---- ---- ----

[ EDITOR'S NOTE (2): as an additional follow-up, I asked the CDNS guys to give me

a briefing on exactly how Virtuoso Studio did process migration. My notes follow.

Fun Early History: Process migration EDA SW has been around for over 20 years.

Cadence even bought Q Design Automation for $9.2 M (cash) in 2004 to do it.

It had so-so success with the big guys. It was an expert heavy tool requiring

massive CAD support. Every new CMOS process migration was a TON OF WORK. Meh.

Fast forward 20 years to 2024, here's what Beckley's R&D guys have created:

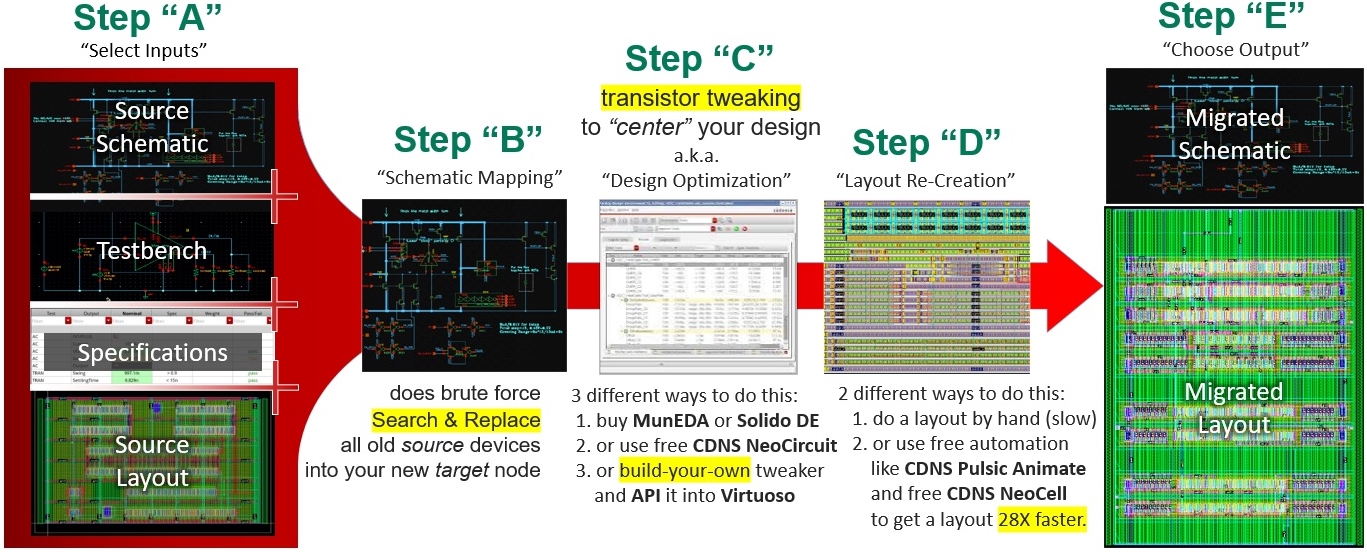

Starting from a high level, migrating your custom IP to a smaller node goes:

A. Select Inputs source schematic, testbenches, specifications, and layout

B. Schematic Map your devices with parameters

C. Circuit Optimization to optimize and "recenter" your design

D. Layout Re-creation and then extraction through custom automation

E. Choose Output your target migrated schematic with its layout

(click on pic to enlarge image)

|

Step A. Select Inputs is where you bring in your source schematic,

source testbenches, source specifications, source foundry libraries,

and source layout from your original.

---- ---- ---- ---- ---- ---- ---- ---- ----

Step B. Schematic Mapping is a brute force first pass "search & replace"

applied across your many source devices to roughly translate them into

your new target process node's technology. It's like a crappy early

version of Google Translate but for analog designs -- that generates

bad unity gain frequencies, ugly slew rate mismatches, out-to-lunch

phase margins, and power specs that are way off -- but it's a starting

rough design translation.

(I call this the "Stupid Monkey" phase of process migration because you

end up with a horribly broken design mapped into your target node.)

---- ---- ---- ---- ---- ---- ---- ---- ----

Step C. Design Optimization is what I call "transistor tweaking" where your SW

cleans up all those horribly broken parts of your freshly mapped design.

The Analog Nerds call this "design centering the schematic" (or they like

to brag how "their schematic is meeting spec" when talking to management.)

And there's 3 ways to "center your design" (or do "Design Optimization"):

1. use an off-the-shelf outside 3rd party commercial "transistor tweaker"

like MunEDA Wicked or Siemens Solido DE.

I have no recent user benchmarks of which is better, so it's my

guess that both do "transistor tweaking" well -- or users would

have been warning me how bad X was, or how much better Y is ...

("No bad news is good news.")

2. Or use Cadence's own internal "transistor tweaker" that comes free

with every Virtuoso license. It's basically a perpetually updated rev

of NeoLinear NeoCircuit that Ray Bingham bought in 2004 (according

to Jim Hogan "for roughly $100 million" -- mucho $$$$ back in 2004.

Now $100 million will get you 2 or 3 homes in Mountain View.)

It's the part of Virtuoso that permutationally tweaks all the widths,

lengths, fingers, M-factors, # of fins, stacking factors, resistances,

capacitances, device types in your devices to meet your spec.

Fun Fact: each time you use this particular pull down menu inside of

the Virtuoso environment, you're actually launching some updated

flavor of NeoLinear NeoCircuit inside of ADE!

3. Or build your own in-house "transistor tweaker" and plug it into the

Virtuoso Studio ADE through the CDNS proprietary SKILL API.

You may think this build-your-own tweaker/API approach was put there

for the sad nerdly EDA-writing academics to give them something to do

on their sad, lonely Friday nights ... but you'd be horribly mistaken!

In real life, this do-it-yourself transistor tweaker/API approach is

crazy popular with Big Guys like Apple, Intel, Samsung, MediaTek.

Why? The Big Guys each have huuuge internal EDA SW teams dedicated to

making their own Artificial-Intelligence-enhanced in-house "transistor

tweakers" specific to their own circuits and their own style of design.

And if you're doing AI, your AI is only as good as the data you give

it to learn from.

Nooooooooo way is Apple/Intel/Samsung going to let outside 3rd party

AI EDA developers access their massive internal design archives -- to

learn to be a REALLY good "transistor tweaker" -- only to have their

worst rival buy that NEWLY SMART "transistor tweaker" against them!

Roll-your-own "transistor tweaking" (plus API into Virtuoso) means

you keep 100% control of your own internal AI training archives and

you're not helping your competition makes better chips against you.

Regardless of how you get there, your end result after transistor tweaking

is you get a functionally working schematic that "meets specs" in your

target technology -- problem is you have NO layout and bullshit estimated

parasitics -- or even no parasitics at all! -- for your new target design.

---- ---- ---- ---- ---- ---- ---- ---- ----

Step D. Layout Re-Creation done by hand looks like:

1. generate all the devices from your new working schematic. These

are all transistors, resistors, capacitors, inductors.

2. generate all the pins and power rails from your new working schematic.

3. group the devices into modules for structures like DiffPairs, cascodes,

current mirrors, common sources, active loads, stacked transistors,

resistor arrays, cap arrays, matched FinFET devices, etc.

4. place the instances of the modules in the block.

5. hand route all the critical nets (paracitically sensitive nets like

differential routes, shielded routes, pin-to-trunks, busses.)

6. route all the non-critical nets.

This usually takes the Layout Engineer in Noida up to 7 days to do, while

the stupid Analog Nerd in San Jose has been doing SPICE runs with BS estimated,

or even without parasitics getting horribly misleading gain and offset results.

Layout By Hand

Layout By Hand

|

Automated Layout

Automated Layout

|

Now, presto-change-o, this is all whiz bang automated in Virtuoso Studio and

it now only takes 6 hours to do.

BECKLEY'S SECRET SAUCE IS PULSIC & NEOLINEAR

... and OK, before you call B.S. on this 28X faster Layout Re-Creation

with Virtuoso Studio claim, let me back it up with how CDNS does this.

To begin with, CDNS has developed (or acquired) at least 6 to 8 custom PnR

tools over the decades that are used for layout migration -- however that's

NOT their secret sauce.

Last year CDNS acquired Pulsic in early 2023 for $60 million. Pulsic had

been tirelessly working this analog-PnR-needs-schematics problem since 1999.

Beckley bought Pulsic for Pulsic Animate -- which takes one arbitrary

starting schematic and makes 50 good starting possible layouts from it.

They called it "analog virtual prototyping" at the time and it was a sweet,

sweeeeet add-on to Virtuoso.)

Being part of CDNS gave Animate instant foundry access for the sexy 7/5/3/2nm

nodes -- plus that much needed "gate-all-around" buzzword compliance.

Now add in NeoLinear NeoCell which does Step D #3 above ("group into modules"

or "ModGens") or automatically using "layout templates". (Sweeeeeeeet!)

In short, by using Pulsic Animate, Cooper & Chyan VCAR, NeoLinear NeoCell, and

the CDNS R&D incubator "Catena" that Ted Vucurevich spoke of back in 2006,

is how Virtuoso Studio does an automated 6-step layout-re-creation (above)

that's 28X faster than doing layout-re-creation-by-hand.

---- ---- ---- ---- ---- ---- ---- ---- ----

Step E. Choose Output of target migrated schematic with its layout

Once you get a layout -- or you generate those 50 prototype layouts from

Animate (buried inside of Studio), you can then choose the best 5 that meet

your post-parasitic extraction and resim specs; and either you're done! (Yay!)

Or more likely you're going into the minor tweaking zone; which why Beckley

was humble bragging on the DAC'23 Troublemakers panel about his Virtuoso

Studio doing analog/full custom/AMS design process migration:

"So, it does work, John. Does Studio do everything completely? No."

"Does Studio do maybe 80 percent of it? Yes.

"And that's huge."

- Tom Beckley, CDNS Analog Design Big Wig, (DAC 07/10/2023)

And this is why I replied back to Beckley then: "yea, that's huge." - John ]

---- ---- ---- ---- ---- ---- ---- ---- ----

[ EDITOR'S NOTE (3): I've heard rumors that CDNS R&D has some sort of uber super

duper secret AI/ML project called "Merlin" that's supposed to use AI/ML to

close that loop between custom schematic and custom layout.

That is, from those 50 good layouts, it intelligently chooses the Best 5, then it

intelligently respins those Best 5 to make 50 new layouts, then back to step 1.

IF YOU KNOW ABOUT "MERLIN", CONTACT ME!!! YES, YOU WILL BE ANON!!!! - John ]

---- ---- ---- ---- ---- ---- ---- ---- ----

Related Articles

2017: Dan Clein's status of Virtuoso, Custom Compiler, and Pulsic tools

2016: What's REALLY up on new CDNS Virtuoso ADE and SNPS Custom Compiler

2014: SCOOP IV -- Pulsic to launch on new schematic-to-layout tool at DAC'14

2006: Ted Vucurevich on CDNS R&D incubator "Catena" & Space Based Routing

2006: No, Pulsic is not a DFM company and No, Pulsic is NOT on a death watch

2005: analog designers first impressions of new Pulsic Lyric at DAC'04

2004: 9 CDNS execs plus Ted Vucurevich field Cooley interrogation at ICU'04

Join

Index

Next->Item

|