( ESNUG 595 Item 8 ) ------------------------------------------------------- [02/02/24]

Subject: Prakash on DFT static signoff tool -- plus 25 years of Real Intent

The live DAC'23 Troublemakers Panel

Cooley: Prakash. I notice you have a DFT checker. Why would I buy something that

already exists in the other SNPS/CDNS/MENT tools?

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

Prakash: Just a small digression. You were earlier talking about 40 years of

wandering in the desert -- it's the 25-year anniversary of Real Intent.

So yes, I've been crazy for a little while ... and enjoying it for a

little while.

Cooley: You've been a "startup" for 25 years?

[laughter]

Prakash: Yes, we've been a "startup" for 25 years.

Costello: The burning bush is very close.

[laughter]

Cooley: So, in 15 more years, you'll be in the Promised Land.

[laughter]

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

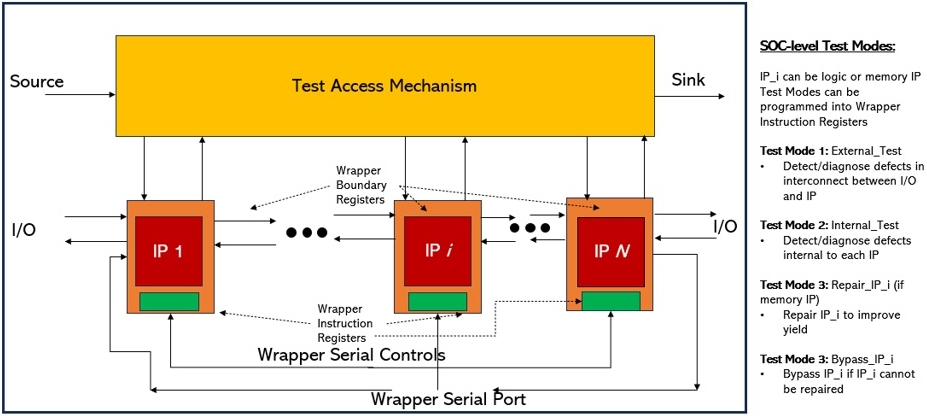

Prakash: To set the context for your original DFT question, Real Intent is

all about "shift left" and static sign-off.

Today, if you look at AI chips, they're building a massive amount

of compute grid. And on a different spectrum, if you look at

automobile chips, they have big massive reliability requirements.

Effectively, if you have problems on the chip -- you will have

to diagnose, and you have to recover, and to repair.

(click on pic to enlarge image)

|

And all of this has to be built on top of your DFT infrastructure.

And so, DFT used to be an afterthought. But now it's becoming a

part of the fundamental chip architecture. And this falls into

Real Intent's sweet spot of enabling "left shift" or "shift left"

outlook -- which is our tools do the earliest possible verification

of a design step.

Cooley: But how do you compete?

(click on pic to enlarge image)

|

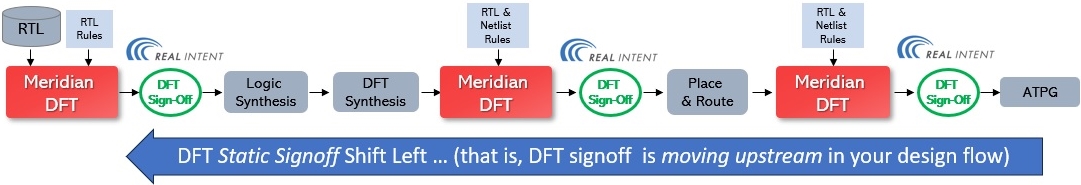

Prakash: We are in a totally different place than SNPS/CDNS/MENT. Our Meridian

RTL DFT tool lets you ensure that at the architectural level or the design

level, that your test and DFT principles (or modes and methodologies)

are all well put together -- and will stay that way as your design flow

goes from RTL to synthesis to placed-gates then to place & route.

Now on the backend side -- the test CAD software, the massive infrastructure

that does scan/ATPG/BIST that SNPS/CDNS/MENT does -- we don't compete there.

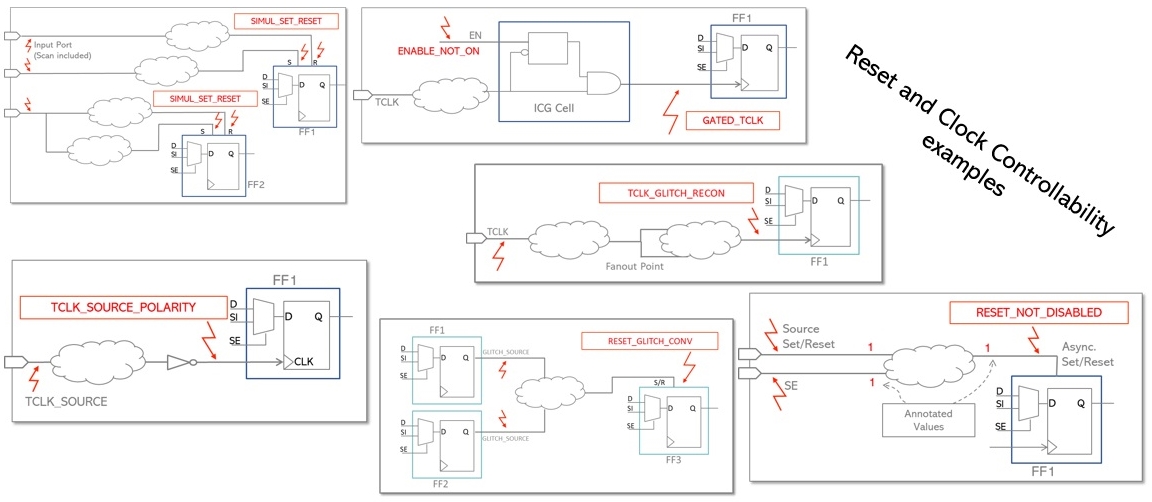

[ Editor's Note: For example, Meridian DFT will, in a single run, verify

multiple test modes for

- Controllability, polarity and glitch issues on asynchronous sets/resets

of flip-flops and on test clocks reaching flip-flops

(click on pic to enlarge image)

|

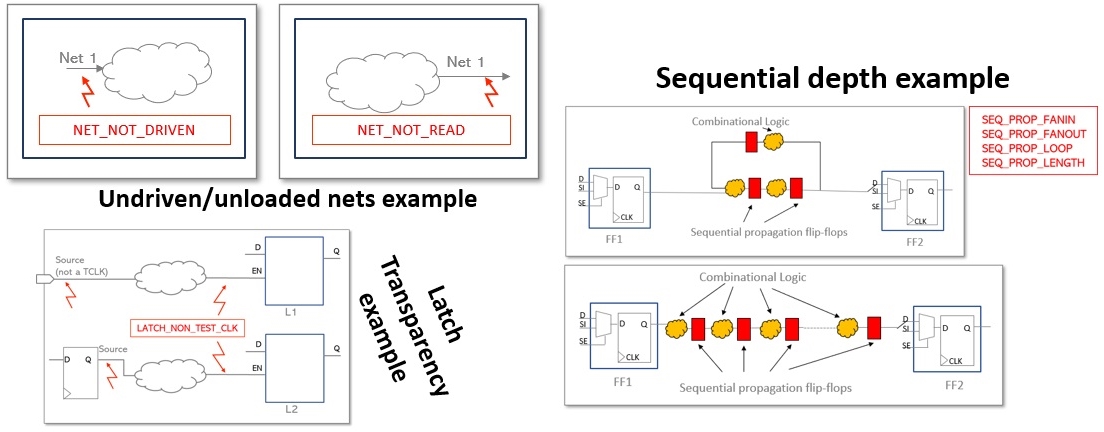

- High sequential depth through non-scan flip-flops and other connectivity

checks and latch transparency checks

(click on pic to enlarge image)

|

- Early detection of control/observe test point candidates

- Random pattern resistance analysis

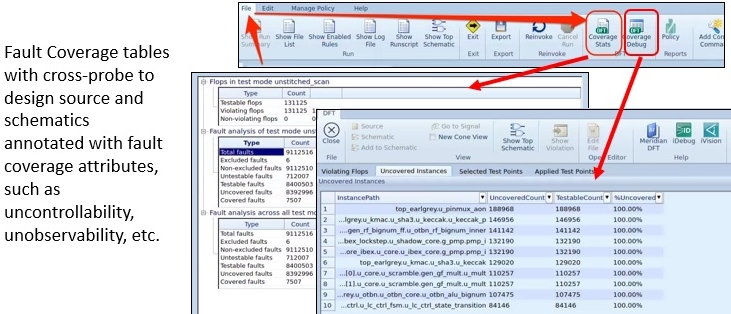

Plus "fault coverage analysis with and without test points, that are

(click on pic to enlarge image)

|

per test mode or overall, with actionable fault coverage debug guidance

to the user -- while checking 100% of the targeted DFT failure risks

under all test modes." - John ]

We, at Real Intent with our Meridian DFT, are simply looking to provide

the best and the most efficient DFT verification at the RTL level by again

the capacity, performance, customized debuggability -- and also early

identification of design test points -- so that the coverage requirements

can be planned up ahead.

And this is the niche that we are doing in DFT -- and in partnership with

customers. And we find that there is a very interesting need for it

in the marketplace.

---- ---- ---- ---- ---- ---- ----

Related Articles

Prakash on Real Intent CDC, RDC, DFT, Lint static sign-off changes

Real Intent low noise/multimode Meridian RDC gets the Best of 2020 #3a

Users choosing Meridian CDC over Spyglass CDC gets the Best of 2020 #3b

Real Intent Verix CDC true multimode analysis gets the Best of 2020 #3c

Join

Index

Next->Item

|