( ESNUG 584 Item 4 ) -------------------------------------------- [06/19/18]

Subject: User reviews new Helic Pharos EM crosstalk tool vs. Ansys HFSS

First, here's Helic Exalto vs. Ansys HFSS tool, considered by many as the

reference 3D EM crosstalk tool on the market.

As the table illustrates, Ansys HFSS cannot handle large designs on silicon,

but does well in package and PCB. The real life silicon capacity, memory,

and runtime constraints often lead to HFSS dropping important (under 16nm)

details about the design and its surrounding environment. This can hide the

effects of crosstalk leading to the wrong conclusion.

- Yorgos Koutsoyannopoulos of Helic

Yorgos on Helic vs. PT-SI, Ansys HFSS, and Star-RC

From: [ Q from Star Trek ]

Hi, John,

I would appreciate it if you could keep me and my company anonymous, should

you choose to publish this. Thanks.

I think it's interesting Yorgos mentioned HFSS in his DeepChip correction

of you. After looking at Ansys HFSS, we very quickly jumped over to his

new Helic Pharos tool that he's announcing at this DAC.

We're designing a 112G SerDes chip in 7nm TSMC. Naturally, it's a mix of

analog PHY plus a lot of DSP spread throughout. We use lots of inductors

and electromagnetics (EM) in our oscillators and gain stages. Our chip

has 8.5 million nets and 50 million total devices.

For tools, we're an all-Cadence house. Virtuoso, ADE, and Quantus for the

analog side. Genus, Tempus, Quantus, Innovus for the digital side. Using

Cadence for analog was a no-brainer because they own that space. On the

digital side we used to be Design Compiler, Primetime, Star-RC, ICC2. But

after we saw how tight Tempus/Quantus correlated with PT/Star-RC, we felt

it was safe to go all-CDNS on the digital side, too.

PHAROS CAPACITY & SPEED

Because of it's amazing capacity (2,000 ports, matrices of 100 Billion mutual

inductance paired nets) the new Helic Pharos allowed my team to save about

30 days identifying our problematic high EM crosstalk nets that could not

have been found using HFSS (100 ports, matrices of 100 million mutual

inductance paired nets). To compare the two, using one 1,000 GB server

you get:

Helic Pharos Ansys HFSS

--------------------- ------------------

max capacity: 100 B paired nets 100 M paired nets

max ports: 2,000 ports 30 ports

max mem use: 1,000 GB 1,000 GB

Pharos is like a cockpit for 3-D crosstalk analysis that has a number of

side options added to it. To start, we selected the victim nets that we

feel are EM crosstalk sensitive, set a frequency range of interest and the

number of frequency points to run. (We did frame sweeps of +/- 2.5% off

of our target frequency of 25 GHz.)

Then Pharos analyzed the electromagnetic isolation between our selected

victim nets against all potential aggressors in our design. We did not have

to feed Pharos "suspected" aggressors. It checked all 8.5 million nets in

our design, then it returns a ranking list of all potential EM crosstalk

aggressor nets (from strongest to weakest) per victim net.

These comparative frequency sweep charts also sold us on the idea of needing

*extra* RLCK extraction for EM crosstalk. See that green line? Star-RC,

Quantus, Calibre xRC all equally fall down on inductive EM crosstalk.

HELIC'S SPECIAL EM-ONLY SPICE

For our 112g SerDes design, our design guys had selected 10 high-Q nets on

our LC oscillators as our "victims". These are known to be ripe for EM

crosstalk issues. Pharos took 2 days on a 512 GB machine to find 2 highly

problematic aggressors that paired up with our victims -- which we then

fixed with some shielding and guard banding plus beefing up our VSS straps.

Maybe if we had 30 days to spare we *might* have found these 2 hidden

aggressors, but probably not. Why? Because under the hood, Pharos is

running a full EM extraction along with its own EM-only massively parallel

frequency-domain linear SPICE simulator. HFSS doesn't have this.

The Helic EM extractor, Exalto, generated a physical model that is then

simulated in its EM-only SPICE to show the AC response between our selected

victims and all potential aggressors. Helic R&D had to make it's own

EM-only SPICE because the physical model can be 10's of 1,000,000,000's

of elements! (To check this internal EM-only Helic SPICE, we did some

test runs with smaller designs where we dumped out the Pharos results and

ran it in Spectre to see if the results correlated. It was within 1%.)

On bigger designs like our 112g SerDes, I don't think any commercial SPICE

engine could run our size of netlists (400K nodes, 8.5 M nets, 50 M devices)

with the mutual magnetic coupling k coefficients included. Helic claims

they can do 1,000K nodes if needed.

PHAROS EM CROSSTALK HEAT MAPS

Pharos gave us multiple visual reports to help identify hot areas of our

design so we could fix it before taping out. One such report is a kind of

"EM isolation heat" map.

It's a layout of our SerDes with an overlay of color gradients from red to

blue showing the areas of high to low EM coupling. For each victim that we

selected, it had red markers pointing to high risk aggressor for it. We

used this heat map to isolate paths that we need to investigate. We found

high EM crosstalk on one of the paths was caused by ground loops, which we

were able to fix by breaking them. In my estimation, we never would have

known about these particular ground loops until silicon came back.

PHAROS TEXT REPORTS

We also got text reports from Pharos like the names of nets sorted by level

of isolation per frequency point. We wrote a script to post-process these

reports to pick out the top aggressors in the frequency band of interest and

then relate them to our gate-level netlist. This helped us understand where

was the highest risks were on the chip.

---- ---- ---- ---- ---- ---- ----

A NEW CATEGORY OF TOOL?

While some may think of Pharos as just a very high speed, higher capacity

rival to Ansys HFSS, if you talking to the Helic marketing guy he'll say

Pharos is "an Electromagnetic EM crosstalk risk analysis tool." His points

are:

- Ansys HFSS is for chip package, pin, and leads. It does 30 ports

at most for reasonable runtimes. It's a one run type of tool.

- Pharos takes in your entire silicon. It does 2,000 ports at most

for reasonable runtimes. It did rough EM analysis across our

entire 112g Serdes 7nm TSMC chip to find the EM crosstalk hotspots

in it. Then it lets us zoom-in to the specific local area with

much tighter accuracy.

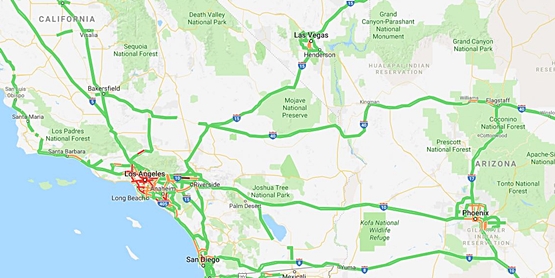

Here's the overall "traffic" heat map for the American Southwest...

And then you can zoom in to...

|

|

It's like doing a car traffic map of the American Southwest, then

finding that Phoneix and Las Vegas are OK but Los Angeles is a mess,

and then you can zoom-in to L.A. to see the details. Pharos does

this. HFSS doesn't.

For me, seeing Pharos handle EM crosstalk on our 8.5 million nets says it's

more of a risk analysis tool than just a higher capacity simulator.

---- ---- ---- ---- ---- ---- ----

Whatever you call it, this new Pharos EM crosstalk tool helped save us

~30 days to tapeout, and it helped us find 2 burried EM crosstalk aggressor

nets that we probably wouldn't have discovered until our silicon came back.

For those two reasons alone, Pharos was worth the price for us.

Kudos to the Helic team for their incredable support and letting me evaluate

this great tool for analog designers. It was well worth writing about.

- [ Q from Star Trek ]

P.S. I asked Yorgos why it's called "Pharos". He said that's the name of

the Lighthouse of Alexandria. "It's one of the Seven Wonders of the

World. Pharos guides chip designers away from EM crosstalk problems."

---- ---- ---- ---- ---- ---- ----

Related Articles

Yorgos schools Cooley on Helic vs. PT-SI, CLK-DA, HFSS, and Star-RC

Helic Exalto gets #7 Best of 2017; because inductance counts at 7nm

Helic's accidental pre-DAC marketing attack on Anirudh's Pegasus

263 engineers on their present day SPICE use and SPICE leaders

Join

Index

Next->Item

|

|