( ESNUG 575 Item 1 ) ---------------------------------------------- [08/08/17]

[ EDITOR'S NOTE: I always love a good critical (versus your usual safe

"happy") analysis of contested topics like FD-SOI vs. FinFET. - John ]

Subject: Dave Dutton critiques the Santa Clara and Japan FD-SOI symposiums

Silvaco Variation Manager is the old Infiniscale IClys which does

Monte Carlo to 50X, and High-Sigma analysis 1,000,000X to 8 sigma.

Supports non-Gaussian. Batch mode library verification, too. They

also have Library Variation Manager that does characteration of 100's

of cells for you.

For example, 28nm FDSOI, 40 cells, 100 corners,

Monte Carlo at each corner, 100's of measures, took 173 mins using

brute force MC and only 19 mins on Library Variation Manager.

ST Micro, Faraday, and Dolphin Integration uses these Silvaco tools.

(booth 1447) Ask for Prashant Singh. Freebie: ear buds

- Silvaco Variation Manager on Cooley DAC'17 Cheesy Must See List

From: [ Dave Dutton of Silvaco ]

Hi, John,

Now that DAC'17 is finally over and I'm on a long flight to Asia, I thought

I'd use this time to finally write up my combined Santa Clara (April 13th)

and Japan (May 31st) FD-SOI Symposium trip reports.

But before I start this report, I must thank you for listing our Silvaco

Variation Manager tool in your DAC'17 Cheesy Must See List. We have a

number of FD-SOI customers who use VM in their flow to do quickly Monte

Carlo and High Sigma analysis up to 8 sigma. It's a money maker for us.

- Dave Dutton

Silvaco, Inc. Santa Clara, CA

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

Event: FD-SOI Silicon Valley Symposium 2017

Santa Clara, CA - April 13, 2017

The SOI Consortium held its annual Silicon Valley Symposium at the Santa

Clara Hyatt in April 2017. This three day event was lead by an evening

executive reception with the Symposium the following day and a well

attended tutorial hosted by Samsung on the third day. Overall it had

282 attendees, with 38% of attendees at the VP or above level.

Naturally, they showcased FD-SOI stories like NXP having already build

three products in 28nm FDSOI production, and then ARM announcing they

fully support designs on FDSOI.

The three FD-SOI fab providers: Samsung Foundry, GlobalFoundries, and ST,

were all there doing Q&A sessions, too.

DUTTON'S FD-SOI RAMPING CONCERNS

Even with the positive advances, there were still some areas of concern as

to how fast is actually FD-SOI ramping. GlobalFoundries would not provide

a true total number of designs on FDSOI and would only answer that they

had "70 engagements" -- what does that mean?

Throughout the day, there was a lot of talk time given to the promise of

IoT, which we have been hearing frankly for years. It almost felt like

FDSOI was the solution to a problem, but that IoT is still yet to happen.

Yes - there are three suppliers for FDSOI, but during the meeting it was

clear that the three fabs are competing and working to differentiate from

each other to the point where backup 2nd source capabilities from one fab

to the other is doubtful.

---- ---- ---- ---- ---- ---- ----

Talk: "How NXP taped out 5 chips in FD-SOI 28nm"

Geoff Lee - SVP & GM Microcontrollers at NXP

Geoff talked about how it was thought that 40nm was the manufacturing limit

for MPUs due to the limit of internal designed FLASH -- but MPUs are now

seeing the need to go to lower nodes like 28nm will drive the need for

embedded memory -- and they can see a path beyond Flash of MRAM or ReRAM.

To get low leakage after trying HighK metal gates, NXP sees FDSOI was the

next step and they jumped in 100%. NXP sees FDSOI as the one way which

gets embedded processing with:

- high performance,

- power efficiency,

- mixed signal, and

- broad scalability

all into one chip. As compared to before where high performance meant MPUs

based on the FinFET nodes. From a Freescale study, NXP sees a path beyond

embedded FLASH to embedded MRAM or ReRAM -- and NXP felt next generation NVM

is here.

NXP gave the most evidence of the show that FDSOI is real with 5 products

taped out and 3 in production. Geoff emphasised that reuse is crucial to

get so many products so fast. Many blocks were reused across his 5 chips.

Showed three FDSOI chips i.MX 7ULP has been out for 6 months. His i.MX 8QXP

is 5X larger, and his i.MX 8QM is 12 times larger and the next will be 20X

larger -- hence the need for future shrink. For their MPUs, NXP was able to

go from a 5x scaling factor to 25x scaling factor which Geoff believes was

only possible with 28nm FDSOI.

The other FD-SOI factor that drew NXP into 28nm FDSOI was its flexable RF

and mixed-signal design properties -- especially its low variation.

Geoff also said their 7ULP product saw 10X lower leakage at same performance

or up to 100X lower leakage at the mid-market use point. They are seeing

peak power of 3W, versus in the past would have seen 12W to 15W.

---- ---- ---- ---- ---- ---- ----

Talk: "How GlobalFoundries FD-SOI (22FDX & 12FDX) will be the Volume Tier"

Alain Mutricy - SVP Product Mgmt at GlobalFoundries

I would have retitled this guy's talk to be: "How Money Changes Everything"

because it was more about the business and cost aspects of chip sales rather

than overcoming specific engineering hurdles.

(click on pic to enlarge image)

|

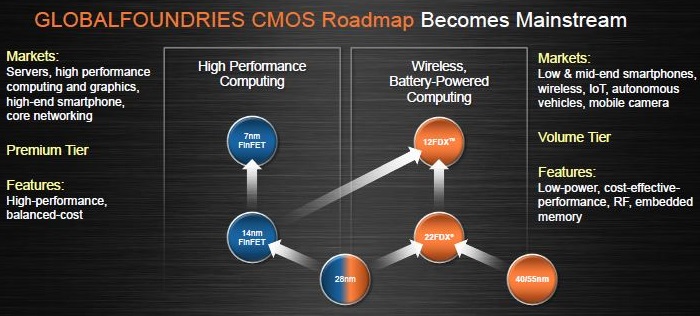

Alain emphasized that although 7nm FinFET can be seen as the Premium Tier

for chip manfacture, GlobalFoundries believes that 22nm and 12nm FD-SOI

will be the Volume Tiers due to the overall shift to more demand of chips

for low/mid-end smartphones, wireless, IoT, automous cars, and moble

cameras beating out the high perf chip demand.

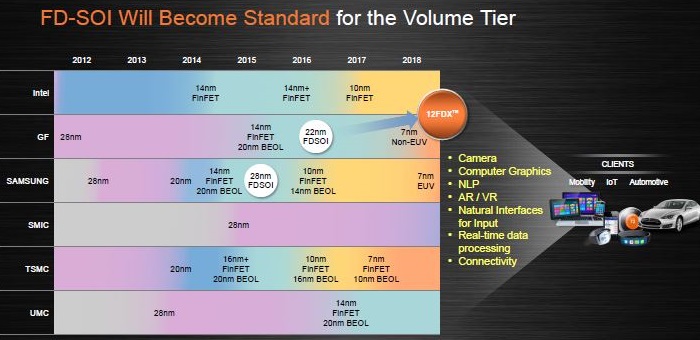

(click on pic to enlarge image)

|

If you look at his slide for areas of growth, look at the semi content for

each sector, you'll see:

For FD-SOI markets: $50B + 34B + 6B + 42B + 8B + 9B + 1B == $144 billion

For FinFET markets: $50B + 6B + 26B == $82 billion

This is assuming that the mobility market is 1/2 high end and 1/2 low end,

plus 100% of data centers and 5G infrastructure goes to high perf FinFET.

Alain later presented two other slides where GF 12FDX would beat out even

10nm FinFET performance "at 50% better power efficiency than 16/14m FinFET",

thus challenging FinFET in the mobility and 5G markets -- but since 12FDX

isn't up for production until 2H 2018, I don't count it in this estimate.

(click on pic to enlarge image)

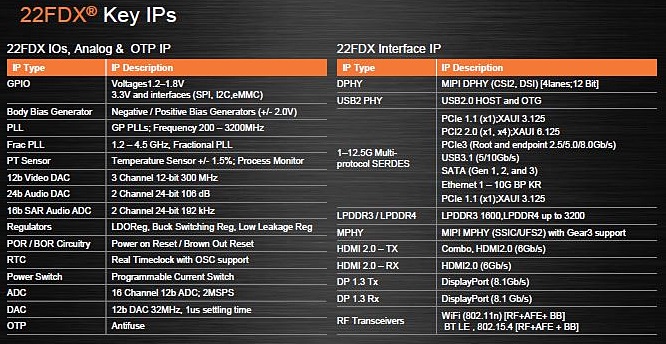

|

Alain pointed out that the battle is for cost which means integration of

mixed signal and RF -- the sweet spot for FDSOI. Globalfoundries has

22FDSOI in production, with a PDK 1.1. They view all their IP is ready

for 22nm FDSOI. Alain said they had 70 active engagements, but would not

give any specific wins at 22nm FDSOI, which caused some skepticism in the

audience -- is it really ready? Later in the Q&A Alain said they have a

number of tapeouts and the first product was in 2016, but still would not

give a specific number.

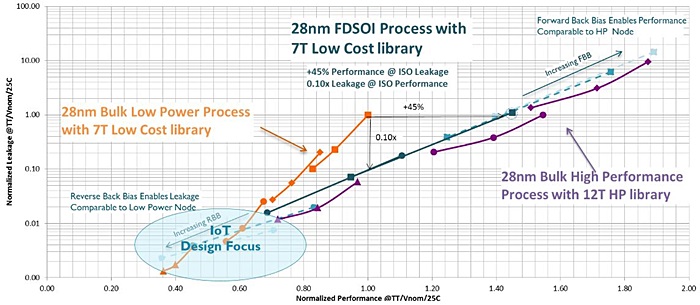

Alain claimed the 22FDX power is less than 1/2 of bulk 22nm and they can

go lower with back bias. GF feels they can get close to the performance

of FinFET node using back bias and stated that 22nm FDSOI is competitive

with 14nm FinFET. Right after this, Alain, said 7nm is still the optimal

node for the highest performance.

GF is investing in FDSOI capacity expanding Dresden and building a new fab

in Chengdu, China. GF has a roadmap to 12nm FDSOI, and stressed that 22nm

is not using dual patterning, and 12nm will be with dual patterning. The

reason they chose 12nm and not 10nm is that below 12nm requires more than

double patterning.

(click on pic to enlarge image)

|

GF has worked to create the ecosystem partners for FDSOI and have the

Big 3 EDA vendors (plus Apache) and their IP platforms ready for their

customers to use.

For 22nm FD-SOI, their main customer testimonials were Fudan, Sigma Designs,

and Dream Chip. And their 12nm FD-SOI isn't even sampling yet.

---- ---- ---- ---- ---- ---- ----

Talk: "How Low Power IP is Essential for IoT and FD-SOI"

Ron Moore - VP of Physical Design Marketing at ARM

This was good talk about how ARM is fully supporting FDSOI and sees IoT as

part of the next growth. Ron pointed out a cumulative 16 billion ARM cores

have been shipped through 2016, and they expect the 100 billionth in 2017,

and they see a path to the trillionth by mid-next decade.

ARM sees mobile still growing but sees smart home, smart city, and auto

combined to drive 1.6X more demand for cores than mobile. ARM did a 28nm

FDSOI comparison on Samsung's 28nm FDSOI and found that leakage was reduced;

and even further reduced with back bias. ARM views FDSOI is real and it

is time to use it, but FDSOI still needs more infrastructure. They see that

IP needs to get more support going, and ARM will build the FDSOI library.

(click on pic to enlarge image)

|

But the Big 3 EDA suppliers have to step up, plus we have to have back bias,

and forward bias for voltage scaling. The SOI consortium needs to organize

and build and IoT reference design. To make these happen, the volume has to

be there on FDSOI for business to invest in it.

I must reiterate from earlier, during the entire conference it was not clear

what adoption level it has -- and until FDSOI's volume ramp is more obvious

to all, FDSOI will continue to see a slow growth of the support EDA & IP

infrastructure it needs.

---- ---- ---- ---- ---- ---- ----

Talk: "The growth of IoT and how it'll impact FD-SOI"

Handel Jones - Founder of IBS

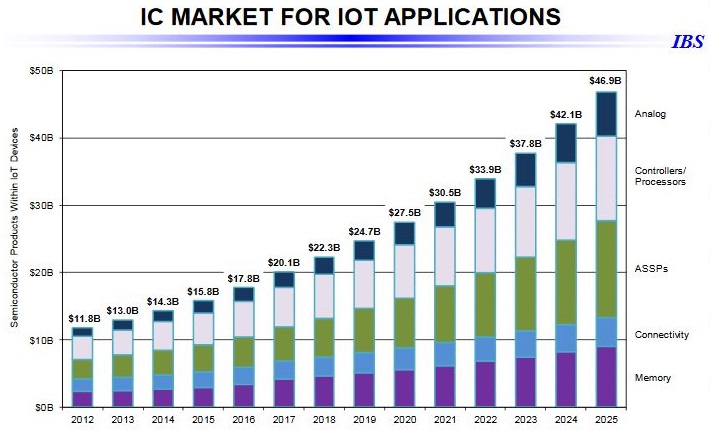

Handel showed a data packed presentation with predictions out to 2025 with

many cases being consistent growth up and to the right. In this industry,

projections beyond 3 year are tough to nail down, so I choose to focus more

only on the 3 year horizon.

After two flat years of 2015 and 2016 for semiconductor, Handel predicts the

market CAGR to be 5.1% -- with most growth coming from the memory price/GB

increase.

(click on pic to enlarge image)

|

IoT, according to Handel, is an era where data is an asset. He predicts

between 2016 to 2020 the number of connected devices will grow from 21.5B

to 41.3B, a CAGR of 14%. For processors, Handel's data shows the shift

from mobile to embedded intelligence and automotive as the bigger drivers.

For control and connectivity, the drivers are mobile and enterprise. For

automotive processers, these will require advanced FinFET or 12nm FDSOI.

For smartphone imaging to support AR, Handel predicts the ISP will fit

the 22FDX (FD-SOI) and 22ULP (bulk) nodes very well.

(click on pic to enlarge image)

|

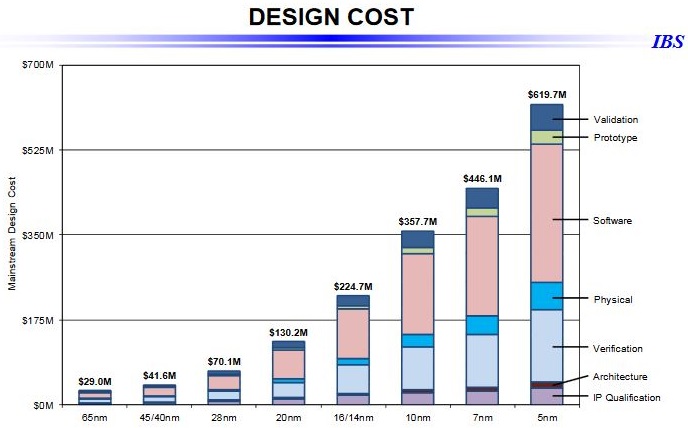

He commented: "What is critical for FDSOI is to show improvement in design

development cost versus performance compared to advanced node FinFET." For

FinFET 7nm has $446M total design dev cost versus $130M for 20nm and $70M

for 28nm. To get a return on the design typically requires a 10X payback,

which for advanced (10/7nm) FinFET the ROI is only achievable for a few

large market players.

Given FDSOI's potential to have comparable performance at the 28nm and 22nm

nodes, the ROI can be dramatically increased. That is the allure of FDSOI,

but it does need to be looked at realistically. About 40% of the total

design cost is for the software, the salaries and costs for writing the

algorithms for the chip design. This should be the same for the design of

a chip for 16nm FinFET as it would be for the similar design on 22nm FDSOI.

If the complexity of the chip design is the same, the software algorithm

costs would be the same.

For example Handel's chart says FinFET design costs would be $70.1M for 28nm

versus $224M for 16nm. The FinFET software cost for the 16nm design is

$100M versus $35M on the 28nm. If you assume the software cost would be

the same for a complex chip originally designed for 16nm if that chip was

redesigned on 28nm FD-SOI, then the dev cost would be $135M FD-SOI versus

$224M for the same in a FinFET. That's a ~$90M savings just for 1 chip!

Handel then explained why is developing FDSOI so slowly. It has recently

shown that it's cost effective. The next hurdle is the capacity issue;

which he says is happening now at Samsung and GF.

After solving the capacity problem, FD-SOI must have IP. That cycle is just

starting as evidenced by ARM's interest. From a year ago to today there is

a lot of progress, but more needs to happen.

Handel predicted next year that a war is starting with TSMC and Intel going

against the 22nm FD-SOI fabs. He also added one differentiator is if you

want to do analog, AMS, RF, or low power -- FDSOI is the best technology.

Handel finished with: "There's a good market for FD-SOI. But... can FD-SOI

build an infrastructure like what TSMC has done for FinFET?"

---- ---- ---- ---- ---- ---- ----

Talk: "Taping out our 22nm FD-SOI automotive vision chip"

Jens Benndorf - COO of Dream Chip

Dream Chip is a fabless engineering company based in Hanover and Hamburg,

Germany comprised of 60 employees. They design camera-based advanced driver

assistance systems (ADAS).

In this talk three use cases for the camera based ADAS were presented:

1.) physical-mirror replacement,

2.) 360-degree top-view camera, and

3.) object or pedestrian detection systems.

The physical mirror replacement (or electronic mirrors) lets you run image

analysis as well as multiview capabilities.

On the feeds from the cameras (the flickering noise generated by the LED

lights) was a design problem which Dream Chip addressed, even when there

are multiple sources of independent flickering noise present in the feed.

Dream Chip also showcased its seamless concatenation of multiple feeds from

different cameras into a single image, for a 360-degree top-view camera.

The third case did pedestrian or object detection using convolutional neural

networks (CNNs). The CNN algorithm is run in parallel on two low-power

processors, interconnected by a Aryeris FlexNoC. Dream Chip said they can

scale this architecture up or down depending on the customer needs.

Dream Chip has had two 22nm FD-SOI tape outs so far, the first on 14/10/2016

and the second on 10/1/2017, both with GlobalFoundries, and both using their

22 FDX technology and ARM Cortex A53 quad core architecture. Their two demo

cars (one actual sized and one toy sized) equipped with ADAS technology were

presented. When asked about the advantages of FD-SOI, Jens Benndorf pointed

to the 2.5x cheaper cost benefit that forward-biased FD-SOI has compared to

the FinFET equivalent.

---- ---- ---- ---- ---- ---- ----

Talk: "Going from 55LP to 22nm FD-SOI for IoT with RISC-V"

Loic Lietar, CEO, GreenWaves Technologies

Greenwaves is a 3 year old fabless French IoT company based in Grenoble

that focusing on selling its "GAP" general platform for IoT applications.

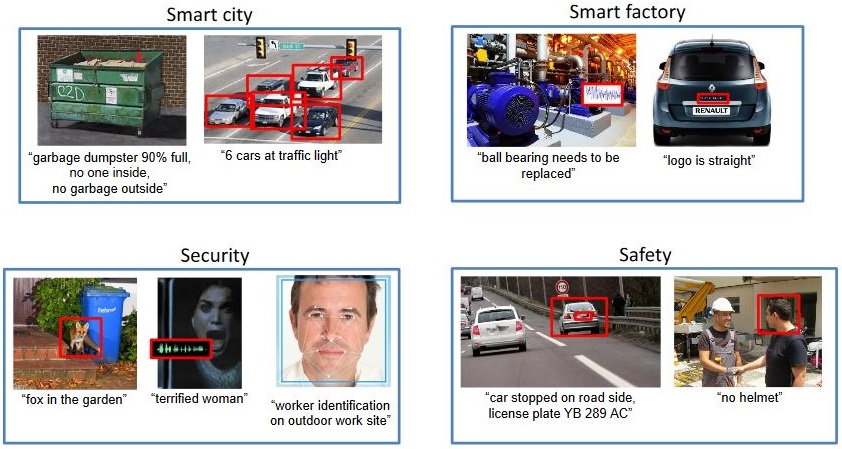

They presented four classes of applications for their GAP:

(click on pic to enlarge image)

|

1. smart city applications, ranging from garbage dumpster monitoring to

counting cars at traffic lights; 2. smart factory, where failure detection

is automated down the assembly lines; 3. security applications, where more

subtle cues such as facial expressions are used to detect a threat; and

4. safety applications, where image processing is used to detect stopped

cars on the road side, or workers at the work site without a hard hat.

Their activity modes break into two dominant modes: monitoring mode, which

accounts for 99.9% of the operation time of the system and uses very little

(uWs) power, and data analysis and communication mode, which accounts for

less than 0.01% of system operation time, but uses 6X orders of magnitude

more power (10mWs) than the monitoring mode.

GreenWaves claimed their nextGAP (which is based on 8 RISC-V processors and

MRAM instead of SRAM) got a 20-fold power reduction by moving to 22nm FD-SOI.

Greenwaves sees production of its GAP8 product in 3Q17, using 55nm LP, and

its nextGAP in 1Q19, using 22nm FD-SOI.

---- ---- ---- ---- ---- ---- ----

Panel: "What's going on TODAY with FD-SOI?"

Wayne Dai, CEO, VeriSilicon

Samuel Geroge, Sr. Director, GlobalFoundries

John Koeter, VP Marketing, Synopsys

Jayanta Lahiri, VP, Invecas

Christophe Maleville, EVP & GM, Soitec

Ron Moore, VP Physical Design Group, ARM

Samir Patel, CEO, Sankalp Semiconductor

Some key take-aways from the panel:

1. How does ARM see their role in the FDSOI? Ron Moore of ARM said

ARM was early participant in FDSOI with IBM. When FinFETs came in

they focused on FinFETS. Now they see FD-SOI as resurgent and

are making sure ARM cores are optimized for FD-SOI.

2. FDSOI is improving, but from an IP perspective the library selection

is a problem for the end user. They need to convert to a smaller

track for the FDSOI, it is different than FinFET. People are still

resistant to get the full use of SOI and using 0 bias versus using

the back bias. We need more support such as from EDA to get the

full use of FD-SOI.

3. SOITEC has developed the whole FD-SOI wafer supply ecosystem over

the last 10 years.

4. Wayne Dai from VeriSilicon commented they witnessed the evolution

of the FDSOI ecosystem. The IP problem is being dealt with quick

enough. FDSOI has become very hot because of IoT. Right now it is

not just cost that promotes FD-SOI, but RF is not easy for FinFET.

Embedded memory is critical. We are moving from 40 to 22FDSOI, so

you will see more IP for FDSOI.

5. General comments on the state of the FDSOI ecosystem. Sam from GF

said: "We are ready, Samsung is ready, NXP and Greenchip have

complicated designs that are done." Samir from Sankalp: "We need

to educate people, the ecosystem is there and it has to go to the

next level." Ron from ARM: "It is unfair to compare the ecosystem

of FDSOI verus 28nm bulk, as FDSOI has only had 7 years. There is

enough in place now." Jayanta from Invecas: "It will get there in

time, but there will be gaps to be solved along the way real time."

6. What is driving designers to take a closer look? John from Synopsys:

"The number one thing is lower power." Samir from SanKalp: "Beside

low power, but also when you go to low voltage the FinFET variability

is huge -- but with FDSOI you can trim and that improves variability.

I think for low power FDSOI will win big." Jayanta from Invecas:

"Porting to bulk to FDSOI is easier than porting bulk to FinFET. In

moving to FDSOI the challenge is to how to take advantage of FDSOI."

Ron from ARM: "The motivation for moving to FDSOI that we hear from

customers is cost. FD-SOI is good enough close to FinFET at much

less cost."

Comments from the audience: "Last year Dan Hutcheson said FDSOI is not

disruptive..." Wayne Dai replied that FDSOI and FinFET invested at the

same time; Intel mainstreamed FinFET, but now FDSOI is becoming mainstream

due to IoT. This is not evolution, it is very significant revolution.

Ron Moore: "There are competing technologies but FinFET just can't go to

low power without a very difficult design." Christophe: "You do not have

to build a complex boat to reach the island, now with FDSOI we have the

bridge."

Wayne from Verisilicon closed with: "7nm FinFET is the sweet spot, 22nm and

12nm FDSOI will also be the sweet spot -- they will coexist, not compete."

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

Event: Annual Tokyo SOI Workshop 2017

Yokohama Landmark Tower, Japan - May 31, 2017

As a follow-up, I also attended the May 2017 Japan FDSOI workshop. At a

high level, while the Santa Clara event was mostly "proof of readiness" and

IoT marketing -- the Japan event was much more about "proof of readiness".

The Japan event had ~200 attendees. Key comments from the Japan event:

1. GlobalFoundries started by showing they now have 80 FD-SOI products

running in their fab -- up from the 70 they claimed 6 weeks earlier.

2. Invecas presented their IP portfolio as ready for FDSOI and that a

customer moved from 28nm Bulk to GlobalFoundries 22FDX and was able

to get 20% less area with lower leakage. They showed a second

customer case where they moved from 28nm to 22FDX and was able to

achieve 50% lower leakage than ULP process, dynamic was 30% less

than 28nm with a 20% area reduction.

3. CEA-Leti showed that FDSOI scaling has been demonstrated down to 10nm.

4. Christophe Tretz from IBM and a Consortium Member stressed that just

moving from 28nm bulk CMOS to 28nm FD-SOI cuts power from 34mW down

to 9mW. Christophe showed a foil where Analogbits was able to get a

5X power savings with 3 month design port from bulk to SOI. He also

showed both established EDA and IP portfolios can support FDSOI.

5. Christophe ended with FDSOI is not the monster PDSOI was 10 years ago.

---- ---- ---- ---- ---- ---- ----

MY OVERALL CONCLUSIONS ABOUT FD-SOI

From these two events, it was clear that FDSOI is progressing and has had

some real design wins -- as evidenced by NXP's "we taped out 5 28nm FD-SOI

chips" in Santa Clara. The vague "we have 70 FD-SOI enguagements in our

fab" claim by GlobalFoundries is nice, but until they and Samsung give more

details I'm not counting any hints at a FD-SOI volume ramp as real.

My concern is that while a basic FD-SOI ecosystem has arrived, it needs to

expand. The FD-SOI ecosystem needs to rival that of the FinFET ecosystem.

It is not there yet. Key advantages like much cheaper die costs, more

flexable AMS/RF features, and lower power is where FD-SOI will win over

FinFET in the IoT world.

Other positives are ARM says it will develope more IP geared towards FDSOI.

And the Big 3 EDA vendors along with Silvaco -- have early capabilities for

FDSOI design in their tools -- and are developing them further.

But Samsung, GlobalFoundries, and ST need to push FD-SOI with the same

engineering zeal and marketing aggressiveness that TSMC did with FinFET,

if FD-SOI hopes to become a viable FinFET rival. Right now they don't.

On the tech side, it bothers me how many engineers are not taking advantage

of back biasing and forward biasing -- and instead they are only doing the

"safe" zero bias FD-SOI because it's what they know. Also, there was only

one mention of how FD-SOI chips could be easily trimmed for variabilty that

can't be done in FinFET. This should have been discussed more but wasn't.

In closing, the answer to whether Handel Jones "we will see a war between

FDSOI and FinFET" is right, or if Wayne Dai "the two technologies will

co-exist with complimentary sweet spots" is closer is yet to be determined.

- Dave Dutton

Silvaco, Inc. Santa Clara, CA

---- ---- ---- ---- ---- ---- ----

|

Dave Dutton worked designing fab equipment for 20 years, then actually running fabs for 10 years, then 3 years ago he found himself in EDA as the new CEO of Silvaco.

|

Related Articles:

BDA, Solido, MunEDA, and Silvaco get #5 for Best EDA of 2016

TSMC has just now 16FF+ certified Silvaco InVar EM/IR analysis

Aart, FD-SOI, Nimbic, Pulsic, SystemC, Jasper, BDA, ARM, not Apple

3D FinFETs mean lots and lots of SPICE runs even with Custom 2.0

Join

Index

Next->Item

|

|