( ESNUG 568 Item 2 ) -------------------------------------------- [03/17/17]

Subject: SCOOP -- more detailed leaked HiSilicon 16FF+ IC Compiler II data

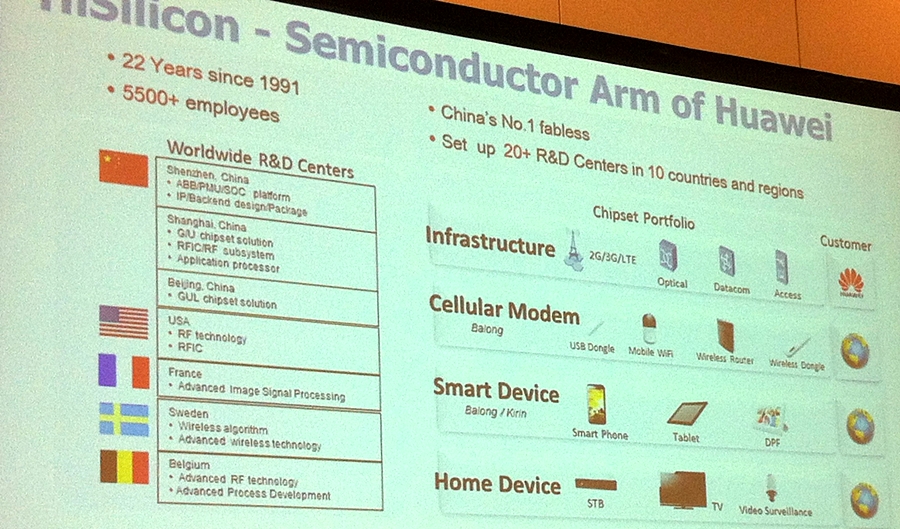

Enclosed are 8 slides from the Synopsys IC Compiler II DAC'16 lunch. It

appears to be a short talk by Huwaei (HiSilicon) engineers about how they

designed their Kirin 955 processor in TSMC 16FF+ quad ARM Cortex A72's and

quad ARM Cortex A53's, at 2.5Ghz/1.8Ghz.

- "leaked HiSilicon 16FF+ ICC2 slides from DAC'16"

From: [ John Cooley of DeepChip.com ]

Here's 15 more slides detailing the HiSilicon Kirin 955 tapeout as initially

earlier described in ESNUG 568 #2. Enjoy!

- John Cooley

DeepChip.com Holliston, MA

P.S. If *anyone* has anon comments they want to add to (or explain) any

of these individual slides, CONTACT ME. I'll edit in your insights.

(And say exactly which specific slide you're commenting on, please.)

---- ---- ---- ---- ---- ---- ----

Slide 1 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 2 -- (click on pic to enlarge image)

|

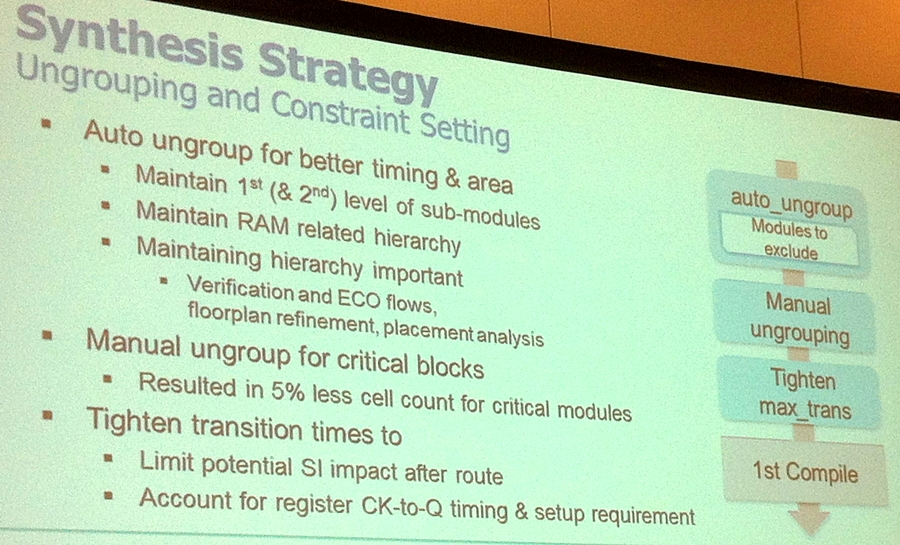

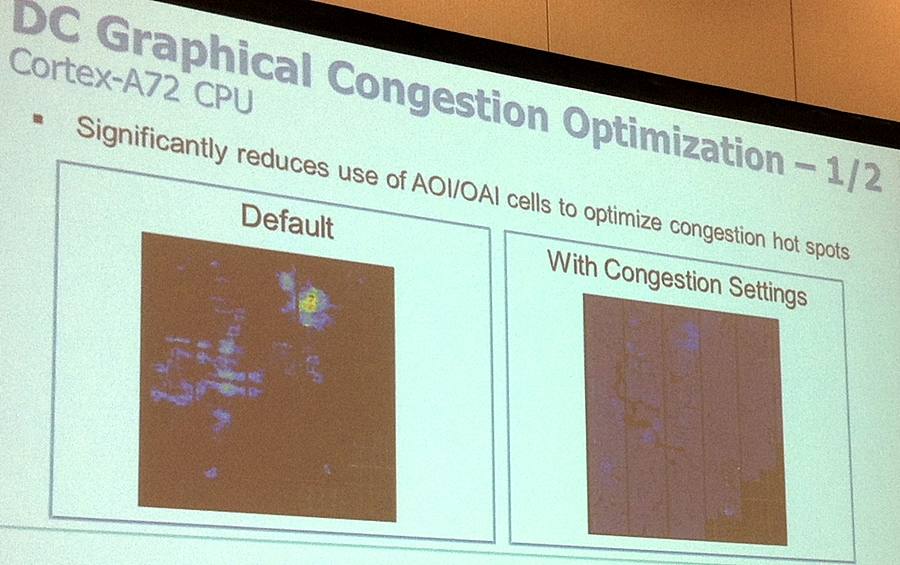

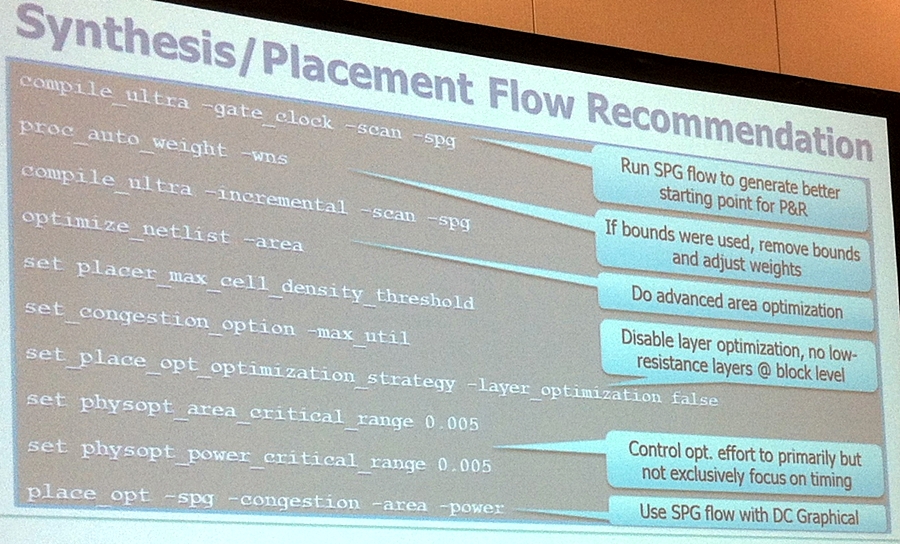

READER COMMENTS: Looks like DC Graphical is being used.

---- ---- ---- ---- ---- ---- ----

Slide 3 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

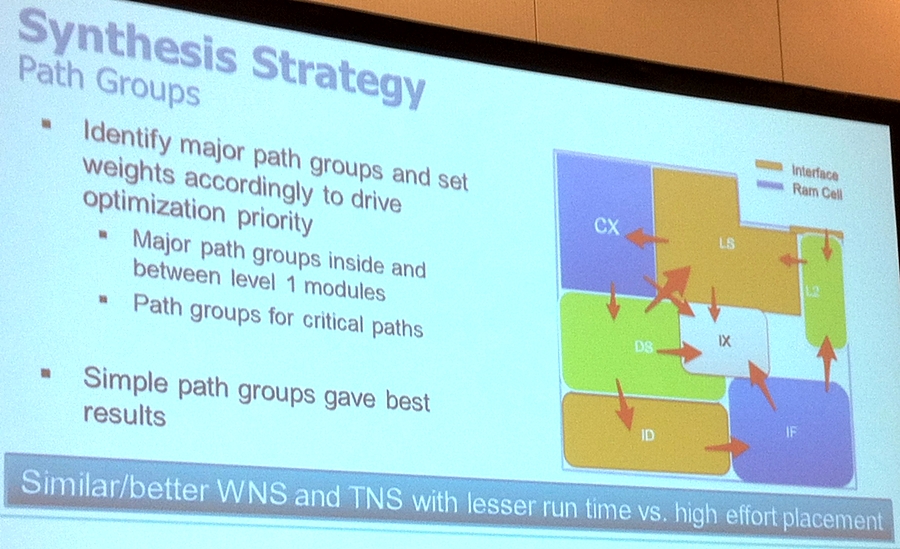

Slide 4 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

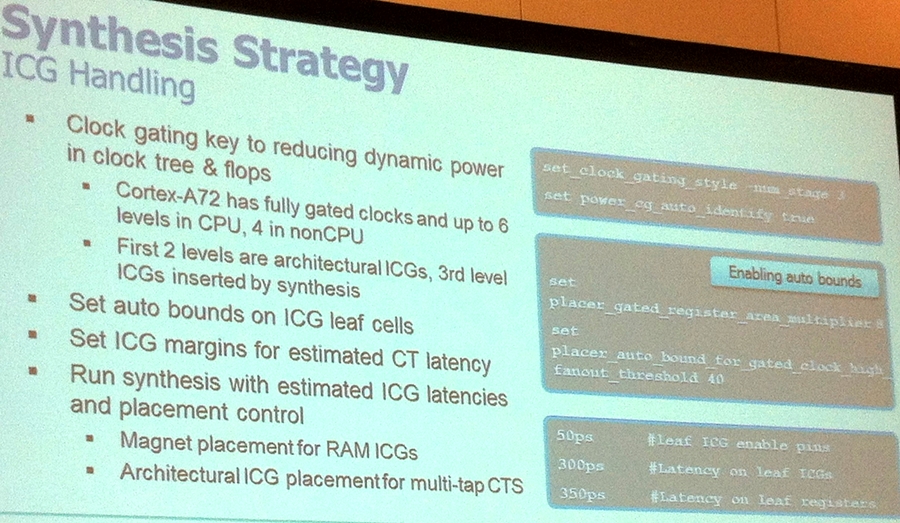

Slide 5 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 6 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 7 -- (click on pic to enlarge image)

|

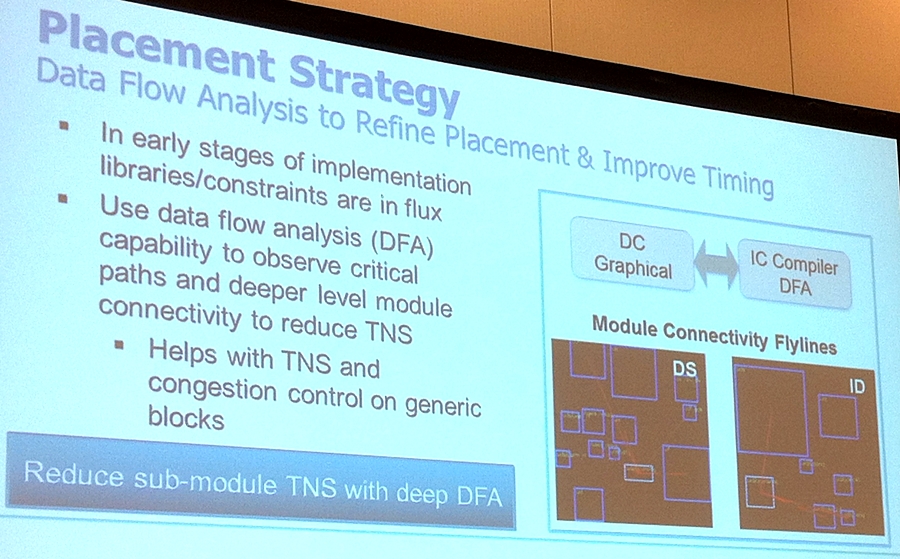

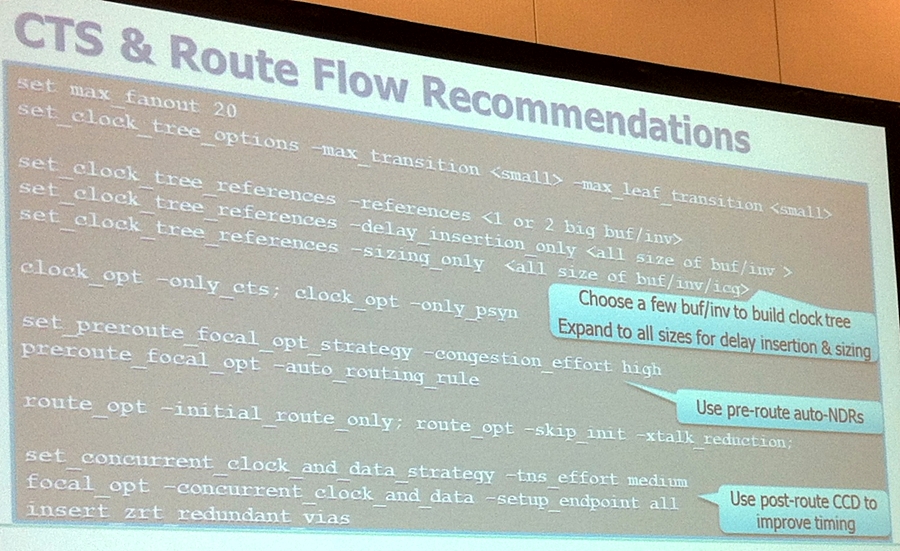

READER COMMENTS: Slide says IC Compiler. Isn't this an IC Compiler II

tapeout?

---- ---- ---- ---- ---- ---- ----

Slide 8 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 9 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 10 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 11 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 12 -- (click on pic to enlarge image)

|

---- ---- ---- ---- ---- ---- ----

Slide 13 -- (click on pic to enlarge image)

|

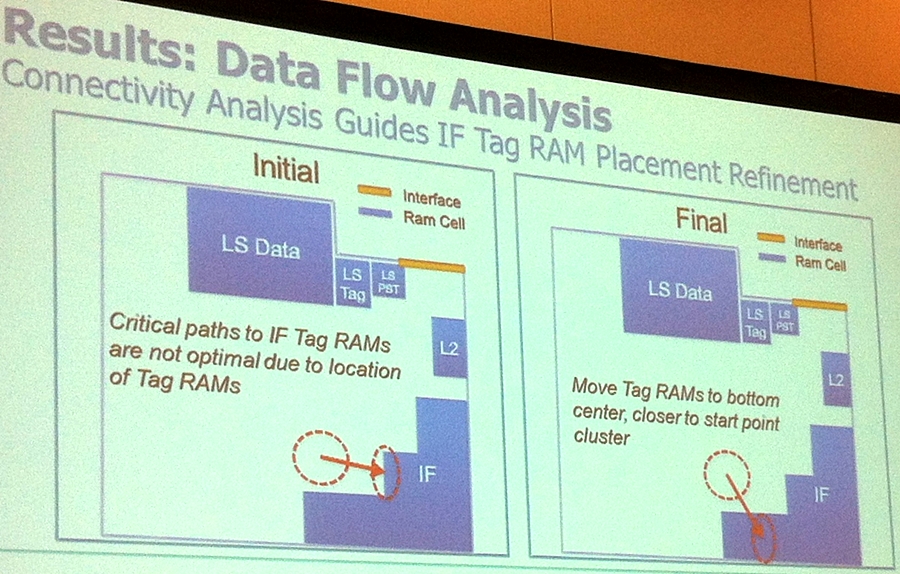

READER COMMENTS: Again it says IC Compiler. Isn't this an IC Compiler II

tapeout?

---- ---- ---- ---- ---- ---- ----

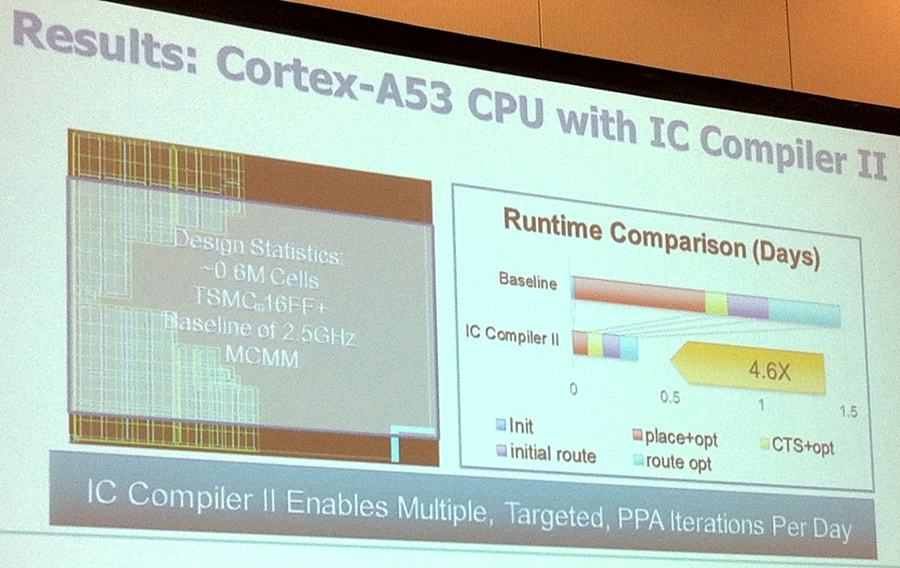

Slide 14 -- (click on pic to enlarge image)

|

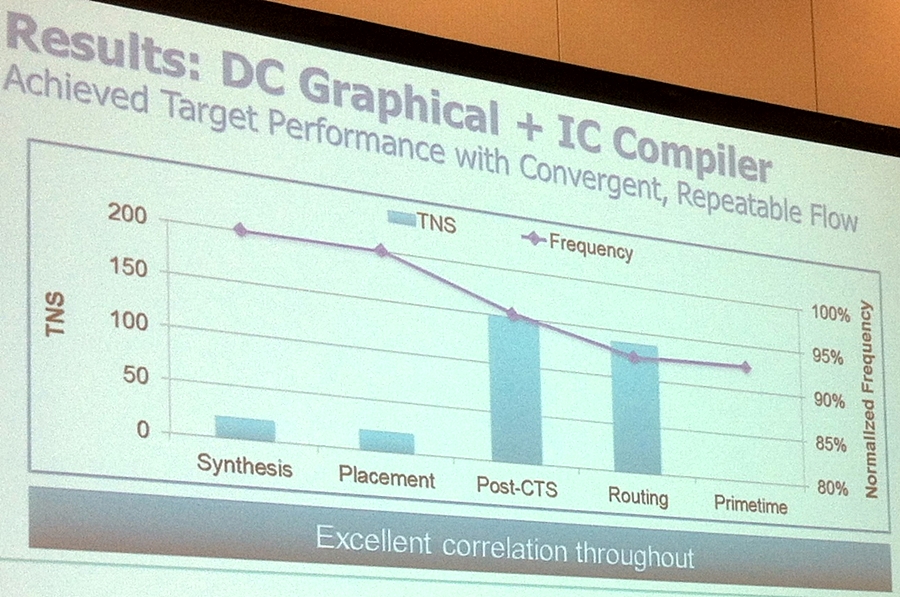

READER COMMENTS: Now it says IC Compiler II?

---- ---- ---- ---- ---- ---- ----

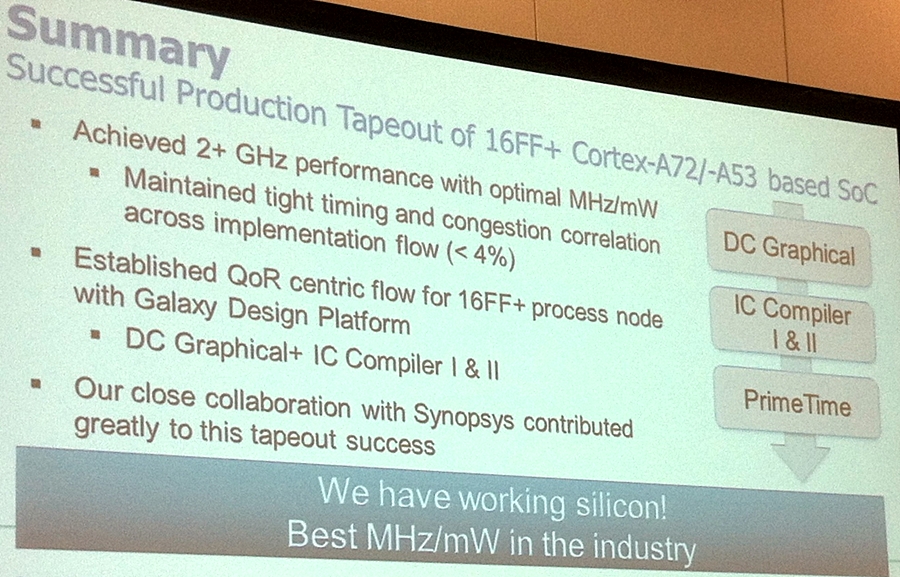

Slide 15 -- (click on pic to enlarge image)

|

READER COMMENTS: ICC used mostly. Only last 2 slides mentioned ICC2.

---- ---- ---- ---- ---- ---- ----

Related Articles

Anirudh and Sawicki on IC Compiler II, Innovus, Nitro-SoC, Antun

The untold parts of that IMEC "world's first 5nm tapeout" story

ICC2 patch rev, Innovus penetration, and the 10nm layout problem

Join

Index

Next->Item

|