( ESNUG 588 Item 23 ) --------------------------------------------- [10/16/20]

Subject: Prakash on functional static sign-off to grow 2X in 5 years, $300M

Virtual DAC'20 Troublemakers Panel

Cooley: Prakash, for years Real Intent has been a linting company.

Now you're going into static sign-off. Is this just another

marketing game you guys are doing to up your prices and

re-sell the same [bleep] under a different name?

Prakash: John, static sign-off is actually a "use model." It basically

is a method for finding 100% of your targeted failures under

all possible test cases.

Products based upon this "use model" have been used in EDA

for a very long time.

Static *timing* analysis -- that is static sign-off.

LVS/DRC -- that is static sign-off.

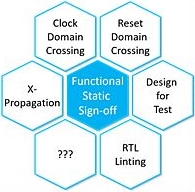

But if you look at *functional* static sign-off -- which is

the category where we at Real Intent are playing -- which

is made up of CDC, RDC, X-Propagation, DFT and lint -- that is

its own category.

It's a $150 million market right now -- and it's driving

Left Shift in the design flows.

I fully expect *functional* static sign-off to double in size

over the next 4 to 5 years. So, it is a very important category

by itself.

Cooley: Left Shift, Shift Left. I think Aart has been talking about that

since I think DVCon 2015.

He's been talking about it about 5 or 6 years now. And suddenly

now you're claiming Aart's buzzwords?

Prakash: We've been doing Shift Left for 18 years.

Prakash: That was the whole premise on which Real Intent was founded --

left shift. Which is to make design flows more efficient and

bring verification earlier (left) --- into sign-off earlier.

So, what do you need to do to enable it? Basically, to enable

Left Shift, of course, first your tools must be used in the

design flows, but they also need to be fast -- and they need to

minimize or reduce the engineering time.

That's the way you're going to make your verification processes

more efficient.

What designers want for verification while designing

|

In static sign-off, we take advantage of two principles.

1. The first is hierarchy. Because hierarchical and

abstraction-driven hierarchical approaches have opportunity

to significantly speed up the runtime and the performance

of the applications.

2. The second one is the debug burden, where it takes special

care to organize the reports. We have hierarchical

reporting where you can drill down deep into the report

for each level of hierarchy, which is then further organized

in a prioritized manner with very fine-grained categories.

All of these allow users to use pattern matching very effectively

to quickly find the root cause of your bug(s).

And using these two approaches, people are coming to us to

support newer static sign-off applications so that they can

further drive their Left Shift.

Functional static sign-off tool today

|

That's what gives me the confidence to say that the *functional*

static sign-off market will double in the next 4 to 5 years.

Sawicki: John, one thing I'd also like to add into that is *you*, John,

talk about it as "linting".

I have to guess on this one is that if you look at what's

happening right now, it's really about formal going into

formal apps. Formal has always been a great tool, but

you had to give people on IQ test and make sure they could show

you their PhD before they could start using this stuff.

|

"Formal has always been a great tool, but you had to give people on IQ test and make sure they could show you their PhD before they could start using this stuff."

- Joe Sawicki of Mentor/Siemens

|

By moving that up front ... you may not like the "Shift-Left"

term but certainly it's to the left when we draw a flowchart of

the design process.

It [*functional* static sign-off] is really changing how people

are doing verification and it's an absolute necessity when

you're trying to verify, within the next couple of years, a

couple of billion transistors of logic on a design.

You're not going to be able to get verification all done through

testbenches, application loads, or anything else. This whole

move to above formal into an application space and moving that

up front -- it's going to be a necessity.

Cooley: Now you're saying you're going into heavy formal or something?

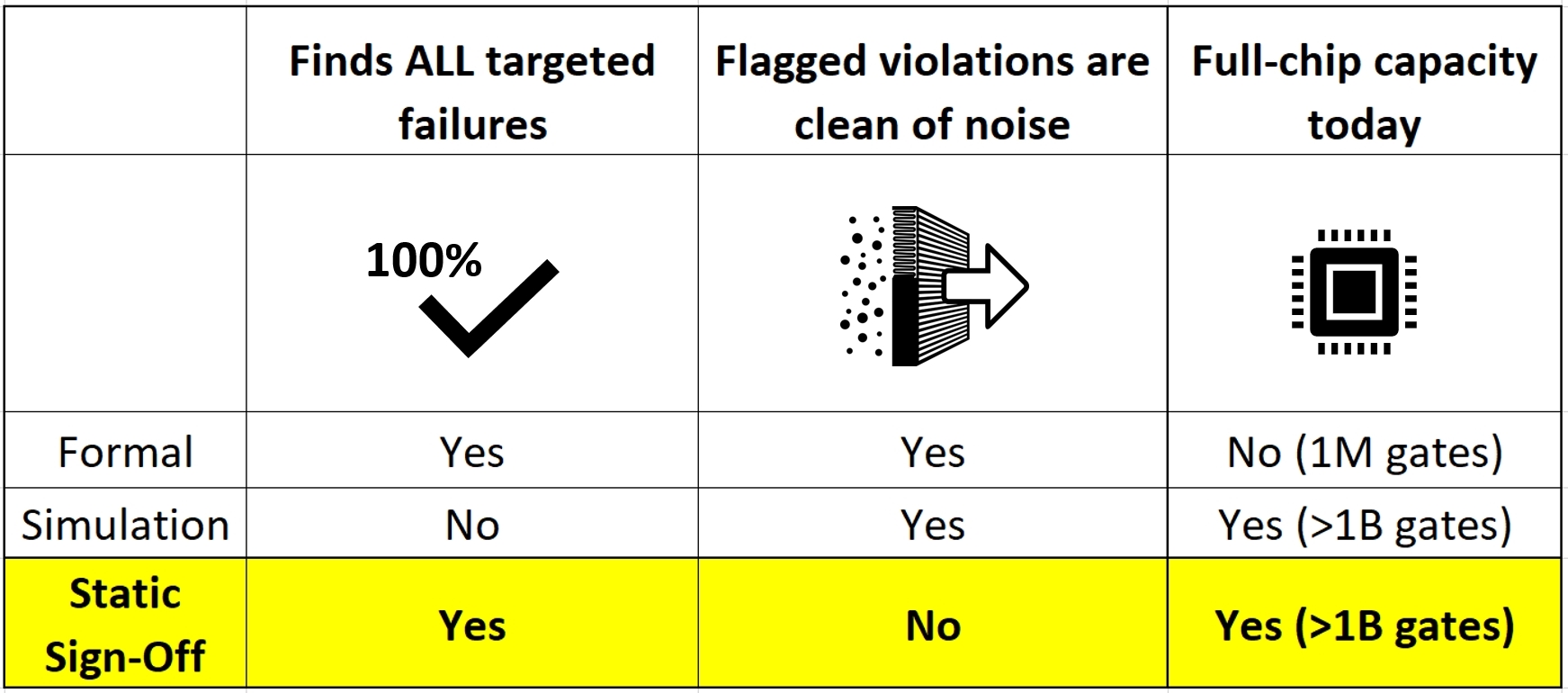

Prakash: So static sign-off technology is different from formal. Let's be

very clear on that.

If you talk about formal, traditionally it's Boolean logic

analysis. And that is not static sign-off technology -- it's

not necessarily based upon Boolean logical analysis. That's

the fundamental difference.

Formal is very precise in the sense that it finds a problem for

you that you're targeting. And you know precisely that it's

a problem. And it can also prove to you that you don't have a

problem in the design.

|

"Most formal applications definitely

max out at 1 million gate designs."

- Prakash Narain of Real Intent

|

The biggest problem with formal is capacity. It does not

complete.

Guess what? Most formal applications definitely max out at

1 million gate designs.

So, if you want to do *functional* static sign-off you have to

look into a technology that is completely different from Boolean

logical analysis. That's the way you scale into a billion gate

transistor designs.

|

|

Formal vs. Simulation vs. Static Sign-Off

|

The trade-off *functional* static sign-off makes is it does not

tell you precisely that you have a failure in the design.

It tells you all potential failures in the design. In the

process it gains completeness and runtime. Then the user has to

debug and say which potential failures are real failures and

which are not.

If you look at static timing analysis [like PrimeTime or Tempus]

as a perfect example. Reported STA violations are:

- on false paths, multicycle paths;

- until you write exceptions, they are all (noisy) violations;

- there are commands built into [PT/Tempus] static timing

analysis to allow you to eliminate these misleading paths.

So, this is the paradigm that [$150M] static *timing* analysis

uses. It uses its own fundamental new set of technology and it's

a totally different use model.

Cooley: Okay. Alright.

---- ---- ---- ---- ---- ---- ----

Related Articles:

Sawicki on his "free" AFS-XT being 5x-10x faster than Spectre-X

Costello on Metrics cloud in 4 hours vs. SNPS/CDNS/MENT's 5 days

Prakash on functional static sign-off to grow 2X in 5 years, $300M

Join

Index

Next->Item

|