( ESNUG 584 Item 3 ) -------------------------------------------- [06/19/18]

Subject: SCOOP -- Anirudh to show Project Virtus to crush Synopsys/Redhawk

I like the ICC2/Redhawk integration.

It's unusual to see two EDA competitors work together like that.

---- ---- ---- ---- ---- ---- ----

Tempus + Voltus:

Tempus and Voltus built on the same code base, i.e. truly integrated.

This is unique. It's the only integrated signoff for STA and signoff

power analysis -- critical for 16nm or lower with low supply voltages,

where you can't just rely on standalone STA and power signoff anymore.

- from Cadence Voltus, Ansys RedHawk, SeaHawk, Tempus, Primetime

From: [ John Cooley of DeepChip.com ]

I didn't know it, but these two user comments from my "Best of 2017" survey

triggered a news scoop for next week's DAC in San Francisco.

From a spy with a known good track record, I've heard that Anirudh will

announce a new signoff tool at DAC'18 code named "Project Virtus". It

essentially blends his Voltus dynamic IR-drop into his Tempus static

timing analysis to make one tool.

Yes, you can still use Tempus and Voltus as separate standalone tools, but

supposedly you'll get better overall ROI if you use their spiffy "new"

merged Virtus combo tool instead.

The background is above 16nm, IR-drop and timing signoff have been loosely

coupled. Using Voltus or Redhawk, a chip designer verifies that his IR-drop

is within X% of the supply voltage and then in Tempus (or Primetime) he

checks to see that his worst-case timing signoff is verified with that X%

reduction in the supply voltage. Each analysis is done separately and often

by different people. Not much cross-communication was needed unless IR-drop

waivers needed further evaluation.

This worked well until around 16nm, gaps started showing up. These gaps

were covered either by adding more timing uncertainty or larger IR-drop

margins. But there is a point where adding margin hits a wall -- where

adding incremental margin dramatically increases the number of failures

and correcting these had a significant impact on PPA.

The chip design world hit this wall at 7nm.

---- ---- ---- ---- ---- ---- ----

7NM NEEDS TRUE SIGNOFF

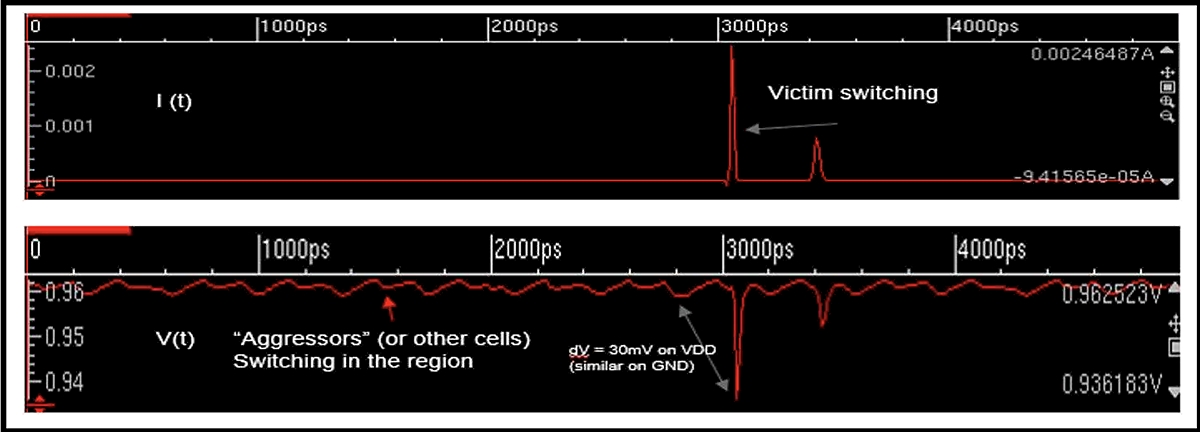

Traditional IR-drop (either Voltus or Redhawk) works on the full-chip level

with a "vectorless" method. A "victim" will have IR-drop analyzed with a

certain percentage of neighboring cells acting as "aggressors" (switching)

and measuring the victim's induced IR-drop. This vectorless method does

not emulate expected logical function but works OK for multiple aggressor

IR-drop on a low-resistance power grid.

At 7nm the power grid resistance is a lot higher than previous nodes.

(click on pic to enlarge image)

|

Notice how the victim's own switching causes IR-drop

Now the IR-drop problem is more localized. The majority of a cell's IR-drop

is self-aggressed or coming from adjacent neighbors. On one hand, higher

PG resistance decreases the radius of aggressor/victim combinations and

isolates some IR-drop problems. On the other hand, certain cells with

unfortunate adjacency, path criticality, and switching characteristics will

have significant IR-drop violations.

Many of these path-specific IR-drop fails WILL NOT be caught using the

(Voltus or Redhawk) vectorless approach. Adding pessimism to the vectorless

approach will create too many false violations that are prohibitive to fix.

Developing an SOC-wide exhaustive switching vector set is not practical.

Even if these vectors are available, the time to run a vector-based IR-drop

analysis would be orders of magnitude (months or years) too long.

WHY PROJECT VIRTUS?

When Anridh came on board in 2012, one of the first things he did in his

massive digital SW rewrite of Encounter was to put everything under one db

and one data model that could go down to 0.5 nm. This made sense for DevOps

cost savings, plus it would give Cadence an advantage over the Synopsys

traffic jam of 7 db's and 7 data models (DC, PT, Milkway, Physical Compiler,

ICC, Volcano, and ICC2) that Aart has to manage in digital implementation.

TIPPING POINT: Most device physics nerds knew the resistance would spike at

7nm from the power grid to the rails from earlier ITRS projections. What

this data from 2013 showed was that at 7nm local interconnect would also

spike, increasing the path delay sensitivity as VDD reduced. Meaning the

IR-drop and delay calcs had to merge at 7nm. Meaning EDA developers had

to merge their IR-drop and STA tools. So from what my spies tell me by

mid 2016 when the actual 7nm data come in, Project Virtus was born.

---- ---- ---- ---- ---- ---- ----

VIRTUS IS SELF-CORRECTING: Virtus works by hunting down the critical paths

that are susceptible to 7nm IR-drop violations, it then calculates the

IR-drop for these paths, then it uses the new more accurate IR-drop supply

voltage to recalculate the critical path delays for these iffy paths. It

has three critical attributes:

* Virtus has Tempus timing signoff and Voltus IR-drop signoff built-in

on the same executable "and operates seamlessly." This is essential

and right now only Cadence can do this.

(Synopsys cannot readily do this with its own 7 internal db's and data

models -- much less adding ICC2 to DC to PT -- and then adding in an

alien outside Ansys (Apache) Redhawk, and then adding yet other

different alien outside (Gear) SeaScape. That's a dumpster fire of SW

rewriting and translating to's/from's between 9 db's and data models!)

* Virtus does "IR-drop corrected" delay calcs in a "new" way. It's yet

to be seen if TSMC/Samsung/GF agrees with this "new" way or not.

* Virtus is not vectorless; instead it uses a "new" IR-drop switching

method that supposedly is "fast, but functionally accurate."

The self-correcting aspect of Virtus comes into play when it is trying to

choose which iffy critical paths to analyze. Choose too many to analyze

and your runtime goes up. Choose too few to analyze and your accuracy is

off. They found that these target paths are not always obvious. It's

more complicated than taking the top few signoff paths. Other paths and

sensitive victims must be analyzed. And the buzzword fix to this is...

MACHINE LEARNING: My spy says Cadence claims to have added Machine Learning

to Virtus to help it determine the minimum sufficient set of critical paths.

But since ML is one of today's Hot New Trends, I wonder if this isn't just

an empty buzzword claim that the Cadence marketing people added to make

their new Virtus combo tool appear more "sexy". "And it's got ML, too!"

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

---- ---- ---- ---- ---- ---- ----

BUT CAN A PRIMETIME-SI PLUS REDHAWK COMBO DO 7NM & BELOW?

To handle this 7nm problem, at DAC'17 last year Synopsys and Ansys announced

their partnership on combining Redhawk and ICC2 for early power analysis.

Buried in the middle of their press release was:

"Synopsys and ANSYS will also provide a feedback loop between the

two-gold standard solutions, Synopsys PrimeTime and ANSYS RedHawk.

Voltage-aware timing analysis can be performed rapidly to avoid

additional guard-banding and design margining."

- joint SNPS/ANSS press release (06/19/2017)

Call me jaded, but at best it will be a Rube Goldberg machine because of

the 7 internal db's and data models SNPS has -- plus the 2 internal db's

and data models Ansys has.

Rube Goldberg's Self Operating Napkin

Rube Goldberg's Self Operating Napkin

|

OK, so let's just pare it down to 3 db's/datamodels. (ICC2/PTSI/Redhawk)

For this to work, RedHawk and Primetime-SI must load the same design in

separate sessions and communicate data model-level information to ICC2

through interfaces designed by SW engineers in rival companies -- and do

all this with signoff level accuracy.

This is too complex even to do as purely R&D and SW support tasks, and not

to mention the between company politics.

"I'm sorry, but that's an Ansys problem. You've got to

talk to them to fix this."

"I'm sorry, but that's a Synopsys problem. You've got to

talk to them to fix this."

Sure, if you're Apple or Intel or Samsung or some other Big Money Tier 1

customer, they'll fix whatever you need. But what if you're not?

---- ---- ---- ---- ---- ---- ----

AND AGAIN, ANIRUDH WAS LUCKY: Earlier I wrote how ICC2's failing in 2013

gave the opening in 2014 for Anirudh to steal the PnR lead from Aart. This

wasn't Anirudh just being "brilliant"; this was Anirudh also being lucky.

Right now there's a tipping point happening with IR-drop at 7nm. And

because of one simple house cleaning DevOps decision made back in 2012 to

put everything in CDNS digital R&D SW onto one db and one datamodel

"because it saves us big $$$ on SW development!", Anirudh can now quickly

merge two of his tools without much hassle to deal with the 7nm issue;

while Aart and John Lee are mired in the "too many conflicting db's and

datamodels" traffic jam. Damn! Talk about Anirudh being lucky! Twice!

See you at DAC.

- John Cooley

DeepChip.com Holliston, MA

P.S. The "GM Salute" was from the June 23, 2014 issue of Time magazine.

Corporate blame passing is an extremely well known business problem.

---- ---- ---- ---- ---- ---- ----

Related Articles

Cadence Voltus, Ansys RedHawk, SeaHawk, Tempus, Primetime, Dorado

Anirudh and Sawicki on iffy Apache IR-drop #'s vs. Voltus/Innovus

A second CDNS Voltus-DP vs. ANSS Gear RedHawk-DMP user benchmark

The Nvidia stealth benchmark of CDNS Voltus vs. ANSS Gear RedHawk

Join

Index

Next->Item

|

|