( ESNUG 575 Item 4 ) ---------------------------------------------- [10/13/17]

Subject: Cliff on PSS, Real Intent, CDC, HLS, Fishtail, IP, Pegasus/Calibre

1.) CALIBRE, STAR-RC, & RIVALS

Two months ago at CDNlive'17, Anirudh Devgan launched a surprise

attack on Joe Sawicki's Calibre DRC/LVS monopoly in ESNUG 571 #2.

NEW! -- Cadence Pegasus DRC "massively parallel DRC engine" runs

900 CPUs linear. 8X/12X faster. For Innovus PnR, does signoff DRC,

incrental DRCs, signoff metal fill, incremental metal fill, timing-

aware metal fill, and MPT decomposition for FinFETs. For Virtuoso,

Pegasus does on-the-fly DRC and metal fill work -- with NO memory

streaming; and dynamically does object creation/editing/deleting

feeback directly to the user. Uses olde factory certified Cadence

PVS decks -- no need to chase TSMC/GF/ICF/UMC for Pegasus decks.

LSF or Amazon AWS cloud, too. Texas Instruments & Microsemi users.

(booth 107) Ask for Manoj Chacko. Freebie: Denali party tix

Calibre nmDRC is the industry's DRC/LVS king with all 7nm tapeouts

today using Calibre for sign-off and they're developing 5nm. It

scales to 2K CPUs for designs and 10K CPUs for manufacturing. It

competes vs. Synopsys IC Validator and Cadence PVS & PVSII/Pegasus.

TSMC, Samsung, GlobalFoundries, SMIC, UMC all use Calibre.

Calibre Pattern Matching replaces text-based design rules with visual

geometry capture and compare. It completes against Cadence Pattern

Analysis, Synopsys IC Validator, Anchor D2DB-PM. It kicks ass on

regular SRAM elements, and for curved structures like analog, RF, and

MEMS. Has Auto-Waivers for visual DRC checks to save time. Also

quickly locates & removes design patterns that are "yield detractors".

Aimed at 10/7/5nm designs. Now does Loop DFM/Compact PRISM for

the Samsung processes. Users are Samsung, GlobalFoundries, SMIC, UMC

(booth 947) Ask for Michael White. Freebie: K'Nex

Silvaco Belledonne compares layout versus layout, quickly finds the

differences with respect to wiring, and tells if diff is important.

(booth 1447) Ask for Jean-Pierre Goujon. Freebie: tote bag

Sage iDRM is a physical design rule compiler. It finds all places

in your physical design where your "test" rule applies -- plus where

it's been violated. It helps make sensible DRC decks. 22nm - 5nm.

(booth 513) Ask for Coby Zelnik. Freebie: pens

Coventor SEMulator3D is a tool for the fabs themselves to simulate

the manufacturing process in 3-D. Virtual fabrication. To test

fab effects. It rivals Synopsys Sentaurus and Silvaco Victory.

Has new "Big Data" analytics. GlobalFoundries, Micron, IBM, Imec

NEW! -- Coventor MP creates finite element & reduced order models

for MEMS to go into MatLab, Simulink, Virtuoso, or Verilog-A SPICE.

(booth 239) Ask for David Fried. Freebie: none

- from John Cooley's "My Cheesy Must See List for DAC 2017"

From: [ Cliff Cummings of Sunburst Design ]

Hi, John -

I think you made a big mistake with your DAC'17 Cheesy Must See list having

the CDNS Pegasus vs. MENT Calibre fight as the "#1 Must See of DAC'17".

"Well, it's not every day that you get to see two normally friendly

neighbors, who've gotten along very nicely for the past 20 years,

suddenly break out into a MTV Celebrity Deathmatch."

If you compare the number of hands-on tool users, the number of frontend

functional verification guys very easily outnumbers the relatively fewer

numbers backend DRC/LVS physical verification guys. I don't have any data,

but I would not be surprised to learn the frontend verif users outnumbered

their backend equivalents by a ratio of 10 to 1.

So to be blunt, *this* is what your #1 Must See should have been:

Breker TrekSoC -- these are the grand daddies of Portable Stimulus, been doing it

since 2008. TrekSoC gens multi-threaded, multi-processor, multi-

memory C tests for cache coherency and uP-memory workload perf.

New power management app, ARMv8 app, and the tool is PSS compliant.

Verdi debug. Users Huawei, Broadcom, IBM, Nvidia, Altera/Intel.

Cavium used it for 3-chip 144 mixed cores in silicon bring-up lab.

(booth 1321) Ask for Adnan Hamid. Freebie: USB cellphone charger

NEW! -- Cadence Perspec is on the DSL side, it's a multi-core ARM

verification library/tool for cache coherency, distributed virtual

memory, low power. "We're swimming in ARM cores, John!!! Swimming!"

Qualcomm, Samsung, Mediatek, Renesas, ST, TI, Infineon are users.

(booth 107) Ask for Mike Stellfox. Freebie: Denali party tickets

Mentor Questa inFact is DSL that "achieves System Verilog coverage

25X faster than old school constrained random test." Generates SV

IP level tests & system level C/C++ tests. It can now import SV

constraints. Users are Applied Micro, Ciena, Microsoft, Microsemi.

(booth 947) Ask for Mark Olen. Freebie: K'Nex

SCOOP! -- Synopsys Mystery PS Tool is rumored to be coming out at

this DAC'17. Unknown if DSL or Breker C++ or something else...

Spies say it's to be roughly based on their Certess Certitude tool.

- from John Cooley's "My Cheesy Must See List for DAC 2017"

You seem confused as how this works, John, so I'll give you a summary

explanation that even a physical design guy like you can understand.

Overall, there are two flavors of Portable Stimulus Standard (PSS)

languages:

- The Breker one, which is C++ based.

- The Cadence and Mentor one, which is called the DSL; which

stands for Domain Specific Language.

Per the vendors, the reason why there are two different languages is

because some (CDNS and MENT) users wanted a simple and concise syntax,

which you can get if you invent a new DSL -- while other (Breker) users

wanted the ability to use a C++ library.

This is analogous to the split we see with System Verilog (basically a

DSL/HDL) and SystemC.

Brekker claims that their users demanded a C++ implementation within

the PSS, while Mentor and Cadence claim that most users want a simpler

syntax in the form of a DSL.

Mentor and Brekker seem to have been in this niche the longest; Mentor

with its InFact and Brekker with its C++ implementation.

From what I can tell:

- Mentor InFact is not fully PSS compliant at this time, but I

expect that InFact will be there by DVCon 2018. Mentor has

certainly had the capabilities within InFact, but they now need

to make InFact PSS compliant, and they know it.

I believe Mentor will eventually support both the PSS (DSL) and

a C++ implementation. I was under the impression that they would

translate the DSL code to C++ for those who wanted that capability.

- Brekker seems to be at least partially PSS compliant right now

with the C++ implementation, and this will only improve over time.

I am not convinced that Brekker intends to address the DSL-input

market.

- Cadence Perspec has many PSS-like capabilities and they seem to have

focused on getting it working with their own simulators and accelerator

products like Palladium and IES -- but no mention of it on their

Specman, Protium (HAPS rival), nor Xcelium (Rocketick) tools.

Also they do not mention actual PSS-compliance ever.

I suspect that Perspec will also eventually migrate towards PSS

compliance, but I was not as sure about the timeline for it.

And if Synopsys has anything in PSS it's in 100% stealth mode because I

have not heard them talking about PSS nor touting any PSS products.

---- ---- ---- ---- ---- ---- ----

Here's some of the other things I saw at this DAC that caught my eye:

Cadence Stratus High Level Synthesis (HLS)

Each year I get an update on the Cadence HLS products from both Brett Cline

and Shawn Dart (members of the former Forte team).

Shawn and Brett said that most of the former Forte team is still at Cadence

and that Cadence continues to let them work their magic. The former CDNS

C-to-Silicon filled holes that existed in their Forte Cynthesizer product.

Now they're selling Cadence Stratus HLS -- a combination of C-to-S and

Cynthesizer.

While the Forte Cynthesizer formerly had most of its customer base in Japan,

Brett reported that Japan, although still as strong as ever, now accounts

for 34% of their Stratus business -- so the CDNS HLS business is expanding

nicely in all parts of the world, with the U.S. now being the second largest

region.

The Stratus team has been hyper-focused on implementation and improved

integration with the CDNS Genus RTL logic synthesis (the new name for RC,

the CDNS RTL Compiler) and Genus Physical for early congestion analysis

and avoidance. I don't know how tightly Stratus HLS works with SNPS

Design Compiler, DC Graphical, nor DC-Topo. I didn't ask because it was

obvious they're pushing for their Stratus HLS users to see how design

tradeoffs affect performance, area, power, and congestion using tool data

inside an all-CDNS flow -- instead of spreadsheets and whiteboards (or

with SNPS tools.)

The Stratus HLS product continues to impress.

Mentor Catapult High Level Synthesis (HLS)

I know you and Badru like to trade barbs on DeepChip about his "C Visions",

Badru replies to Cooley's "Cheeky" question about Catapult "noise"

http://www.deepchip.com/items/0572-05.html

but he and I were so busy at this DAC I didn't get a chance to visit his

booth this year. Is Badru's "C Vision" real? I can't tell you.

---- ---- ---- ---- ---- ---- ----

CDC TOOLS

In 2001, I did my first SNUG paper on Multi-Asynchronous Clock Designs (CDC)

and later I did an updated SNUG paper in 2008 on CDC design and analysis. In

2001, I noted that there were no tools to help analyze and check CDC designs,

but as of DAC'17 there were multiple tools addressing this space.

Choosing the best will be in the eye of the beholder, but some interesting

features that I noted are described below. I teach an advanced full-day

course on CDC and FIFO design techniques and it is time to create versions

of this training that incorporate some of the commercial products below.

First point of interest is, do you have very large designs? and if so, are

you going to check the designs hierarchically or flat?

Two tools that claim to handle CDC checking on very large flat designs were

Real Intent and Ausdia. All tools also claimed hierarchical CDC checking.

The second issue is "waivers". When running the CDC tool, how much effort

is spent "waiving" errors that don't really exist. The tradeoff seems to be

spend time up front to reduce time spent later tracking down non-errors; and

adding then waivers -- or getting the CDC tool up more quickly and spending

more time with waivers while running.

Real Intent Verix Multimode CDC

I've known Real Intent tools, along with Prakash Narain and Jay Littlefield,

for many years. The old Real Intent Meridian CDC prides itself on low

signal-to-noise ratio; meaning they want to show you your CDC issues with

fewer messages so you don't have to waste time wading through multiple

repeated or related error messages.

The idea is to have the engineer debug quickly from the CDC tool messages

presented. Real Intent does efficient large flat CDC checking as well as

hierarchical CDC checking.

WARNING: It may take a little more effort to setup the Real Intent tools

because the idea is to avoid the need to do lots of waivers during the runs.

Spend a little time upfront to save on multiple runs later. The tool guides

the user through the setup process.

I know their Meridian CDC well. To quote your Cheesy Must See list: "On

300M gate chip with 103 clock domains, the hierarchical CDC runtime cut

by 5X and memory use cut by 4X." I saw a quick demo of their new Verix

Multimode CDC tool. They made the claims you quoted: "Single set-up.

All modes in single run, no iterations. New static intent verification

finds non-operational clock modes. Vs. Spyglass or Questa, it saves 3.3x

CPU time and 5x engineering time per iteration" -- but since I have not

used the tool myself and I can't vouch for it measuring up to these claims.

Real Intent iDebug pruned annotated schematics

They also demoed iDebug that does pruned annotated schematics to show the

CDC violations.

Real Intent also has a killer linting tool, Ascent-LINT, that completes

nicely with Spyglass.

Blue Pearl Software CDC

Blue Pearl is a CDC tool that is both Windows & Linux-based. The tool does

hierarchical CDC analysis on both SoCs and FPGAs, but most of their users

are FPGA designers. It has a GUI that clearly shows clock groups and

arcs that cross domain boundaries.

The Blue Pearl Software tool can be invoked from Xilinx FPGA SW directly

(creates a Blue Pearl project) and can also be run on Altera & Microsemi,

but Blue Pearl is not built in to those tools.

Their CEO is Ellis Smith. They and Real Intent did really well making the

#2 Best of DAC tool choice last year.

Real Intent and Blue Pearl get #2 overall for Best EDA of 2016

http://www.deepchip.com/items/dac16-02.html

Mentor Questa CDC - the old 0-in CDC

As an amusing side note, if you Google "Mentor CDC" you will first get to

the "Mentor Graphics Child Development Center" web page.

Probably not what you were looking for unless you are a Mentor employee in

Wilsonville, Oregon!

Questa CDC is the old 0-in CDC tool and it always shows well. Questa CDC

touts itself as a quick-setup CDC tool that is well integrated into other

Mentor tools such as UPF Power Intent tools and Questa Formal tools.

Doug Smith of Mentor gave me a quick demo of the Mentor CDC tool to show

its ease of use. Using waivers seemed to be integral to using this tool.

New this year was it's ISO 26262 certified and they added gate-level

features for FPGA CDC. (I guess they're trying to compete against Blue

Pearl SW?)

Ausdia CDC

This is a company I had not talked to before. Ausdia has been around since

2006 and has been in the CDC space for three years. They claim to do very

large flat CDC runs overnight. They had a sign in their booth that said 1B

instances and 5000 clocks. They also have a SDC checking tool.

Synopsys Spyglass CDC

I tried to take a look at Synopsys Spyglass CDC, but failed to connect with

the person who was going to talk to me about the tool. The past couple of

years at DAC, Synopsys seems to be more focused on large group presentations

and the back-rooms seem to be for their sales people to meet customers.

It probably works well for them, but I was hoping to find a schedule of when

I could attend sessions dedicated to tools of interest.

---- ---- ---- ---- ---- ---- ----

WAVEFORM & FORMAL TOOLS

Veritools

First note is that Bob Schopmeyer's son, Mark Schopmeyer was working in his

father's booth at DAC this year. Mark is 31 years old, very friendly, and

a well-rounded individual (hard to believe he is really Bob's son, and yes

that is a dig at Bob.)

Most engineers know about Veritools for their low cost Undertow suite of

waveform viewers for RTL and SPICE runs.

But at this DAC, Bob had a new tool on display called Veri-Parse, and it

may be a future low cost linter. This is not going to be a commercial

frontend tool to compete with Verific, but Bob is taking an interesting

approach where engineers will be able to submit Python code for the tool

to the Veritools web site and this might become a valuable depository and

resource in the future. To be seen.

Veritools also has a very low-cost SPICE viewer that works with the open

source XYce SPICE simulator from Sandia National Labs. The tradeoff

between this free SPICE with the Veritools viewer and SPICE simulators

from the large EDA companies is that the EDA companies have more libraries

already in place.

Agnisys

This is my friend, Anupam Bakshi's company, and it has been around for a

number of years, offering tools and services that help with UVM design

and verification.

The company has multiple tools but the ones that especially catch my eye

are DVinsight, a smart editor for SV/UVM designs, and IDesignSpec, a tool

to help specify UVM Register models. They also have a tool called ARV

used for automatic register and memory verification.

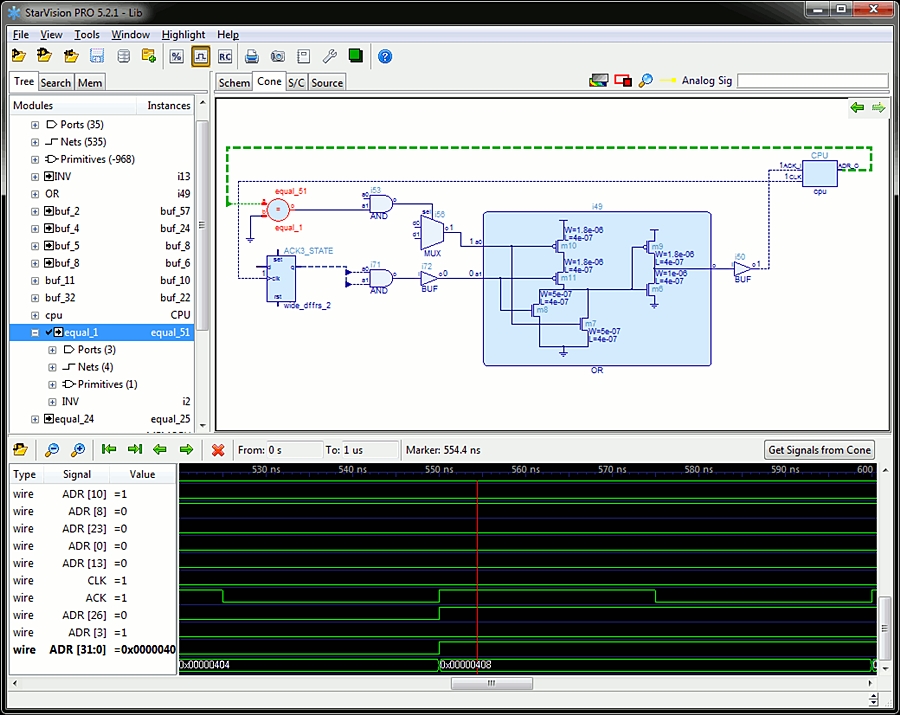

Concept Engineering GmbH

This German company reads Verilog code to quickly create very responsive

schematics for design visualization. It was unclear if the company could

read System Verilog with .* connections to create schematics.

(click on pic to enlarge image)

|

If you have been handed unfamiliar code, this is a great tool for quickly

showing you the schematic of your design. Their digital tool is RTLVision,

while a SPICE version is called SPICEVision. They also have STARVision,

which is a combination of all of their schematic-rendering tools. There are

a number of EDA vendors like Atrenta, Real Intent, Magma, Calypto, that use

them as their graphical frontend. Their U.S. distributor is EDA Direct in

Santa Clara, CA.

OneSpin GmbH

OneSpin had a cool, laid back, coffee shop-like environment right next to

the DAC pavilion this year. OneSpin formal tools this year focused on

ISO 26262 and Safety Critical design, with some new apps that target fault

verification and diagnostic coverage.

Jasper's #1 in #1 "Best of 2016", through killer capacity & debug

OneSpin's #2 in #1 "Best of 2016", the "we try harder" company

Last year OneSpim made a big splash with the users at DAC'16 -- tying

with Jasper for the #1 spot. Their CEO, Raik Brinkmann, is German and has

no fear.

In ESNUG 558 #6, he publicaly corrected Jim Hogan's formal post on DeepChip

last year.

OneSpin also had a Quantify Coverage tool, and they were also talking

SystemC/C++ verification, FPGA-EC and other apps and tools.

Fishtail Design Automation

I have known Ajay Daga for years and for years I had known Fishtail as a

tool that helped check and generate Synopys Design Constraints (SDC).

What I did not know is that Fishtail now does Formal / Assertions. It is

interesting that Fishtail does not try to be the killer-formal verification

tool but it does quick formal checking of a design and then what the tool

cannot prove, it quickly generates assertions to be used by engineers

during simulation to find other problems. An interesting approach!

---- ---- ---- ---- ---- ---- ----

NOT EMULATION, YET NOT SIMULATION

Cadence Xcelium (Rocketick)

The renamed Xcelium is the new-ish Cadence simulator that combines RocketSim

capabilities (this is Xcelium multi-core) and the existing Cadence Incisive

System Verilog simulator.

Nvidia gets 23X faster, 80% less memory with VCS plus Rocketick

IC Manage PeerCache and CDNS Rocketick get #3 as Best of 2016

Anirudh defends JasperGold's rep and the CDNS-RocketSim purchase

It is sometimes hard to keep up with the Cadence marketing team that has an

affinity for changing product names regularly (e.g. CDNS "RTL Compiler" has

become "Genus RTL").

I did not know what Xcelium and Genus were until I visited the Cadence booth

this year.

Xcelium (Rocketick) is now a single core simulator that does X-Propagation and

IEEE Low Power capabilities bundled with the SystemVerilog simulator, and as

mentioned, Xcelium multi-core now includes the highly parallelized RocketSim

simulation capabilities.

Cadence is seeing a 20%-30% performance improvement with their single-core

simulator. SDF backannotation still seems to be missing from the RocketSim

version but is on the roadmap.

Xcelium also claims better Save/Restore dynamic test reload capabilities (a

former Specman feature).

The combined SystemVerilog/Low Power/X-Prop Xcelium simulator will cost

somewhat more than Incisive, but significantly less that Incisive bundled

with Low Power and X-Prop.

Synopsys Cheetah VCS

At their SNUG'17 conference, Synopsys promoted their FastForward sales

program to enables Cadence Incisive and Mentor Graphics Questa users to

migrate over to Cheetah VCS 2017.03. Since I did not see this at DAC'17,

I can't comment on neither its success nor failure.

---- ---- ---- ---- ---- ---- ----

IP & VIP VENDORS

Yes, you have Cadence, Mentor, and Synopsys all doing IP. No news there.

Avery Design Systems

I had good conversations with Chilai Huang, Chris Browy, and Andy Stein of

Avery Design Systems. They pointed out that Avery Design has the largest

Verification IP offering outside of the Big 3 EDA companies, and indeed

their list of Verification IP is impressive. This is probably the one

verification IP provider that you never heard of, but should have!

Side note, Chris Browy is a friend of Stu Sutherland, who just published a

book called "RTL Modeling with System Verilog for Simulation and Synthesis".

The book is hot off the press and was on display in the Avery booth. Stu

is doing missionary service for another 9 months, was not at DAC, and sadly,

he thought he sent copies to Kelly Larson, Chief Verification Technologist

at Paradigm Works (and a good friend of myself and Stu) to be given to

other vendors to display at DAC, but the printer made the mistake of sending

the books to Stu's billing address instead of to Kelly Larson, so Avery had

the exclusive scoop on Stu's new book. It is worth a look. Stu offers the

2nd best SystemVerilog and UVM training available -- behind my training from

Sunburst Design, but if you ask Stu about it, he will probably mix up the

order on #1 and #2!

Truechip

A small verification IP provider with a portfolio not nearly as vast as

Avery's but they tout themselves as being very honest and will tell you

when they don't have the requested IP.

City Semiconductor

A small company that makes Ultra High-Speed Data Converter IP. As a former

Tektronix employee, it always catches my eye when I see high speed A/D

converters.

---- ---- ---- ---- ---- ---- ----

REMOTE SERVER ACCESS TOOLS

Starnet FastX

FastX from Starnet Communications is a tool that caught my eye the past two

years at DAC and it still interests me. Their biggest competitors are

Exceed TurboX and VNC. VNC is probably the biggest competitor overal

because it's free but if remote access and performance are required,

then a company should look at FastX.

This year, Starnet announced that FastX now uses a new open source

technology called WebAssembly or "wasm," which is being developed by the

W3C Community Group that includes representatives from all the major

browsers. Translation: faster remote interaction with your computers.

WARNING: The one issue I had with FastX two years ago was that I never was

able to complete the Linux-version installation and the Starnet support

could not help me. Starnet claims that ease of installation was a major

focus this year as was a faster experience through new web technologies

that are supported by the major browsers. I look forward to trying the

installation again and will report on my success (or failure).

OpenText Exceed TurboX

There are many larger companies who use Exceed remote PC X servers that

should probably look at the newest version of this tool. Their demo in

the DAC booth showed a very graphics-intense interaction with a server

and the speeds were very good. I just need such a tool that interacts

well with simulators and waveform viewers for training.

---- ---- ---- ---- ---- ---- ----

OTHER NEAT STUFF

Duolos EDA Playground

As I mentioned last year, and it is not often that I mention one of my

competitors, but Doulos deserves mention for their EDAplayground.com web

site and making it available to all engineers -- even unemployed ones.

Their web site includes multiple tools that EDA users can try like Synopsys

VCS and Cadence Incisive. I train a large number of displaced engineers on

UVM but the problem has always been that after training, engineers need to

practice and there are no free UVM simulators for engineers to use.

EDA Playground offers a place where engineers can practice their UVM skills.

Continued kudos to Doulos for offering this service to engineers. If you

already have access to a full simulator where you work, you will be much

better served using the full simulation environment.

If I were Wally, I would make it a point to talk to the EDA Playground folks

about adding his Questa tools to their web site.

Verification Academy

As usual, the Verification Academy Booth was a good place to watch useful

tech presentations. I always enjoy the presentations from Harry Foster and

Tom Fitzpatrick.

Harry's presentations always include data from his latest industry-trends

studies, and Tom's presentation pitched Portable Stimulus. I also gave

presentations in the Verification Academy booth on UVM messaging and

proper usage of UVM Verbosities, based on my Austin SNUG 2014 paper on

the same topic.

UVM messaging verbosities are not well understood in the UVM community.

---- ---- ---- ---- ---- ---- ----

NOTABLE ABSENCES AT DAC'17

Xilinx and Altera

DAC seems like a great conference to explore FPGA technologies and tools,

but the largest two FPGA players, Intel-Altera and Xilinx were not at DAC.

Intel was at DAC and I asked at the booth about Altera, but I was informed

that there was no Altera information to be had.

It seems like DAC would be a good place for both of these FPGA vendors to

show the latest capabilities with their tools (and technologies). This was

disappointing.

Xilinx Vivado is supposed to have High Level Synthesis (HLS) capabilities,

but it could not be found at DAC. I think this is a missed opportunity.

Bluespec

I have not seen Bluespec at DAC or DVCon in recent years. Are they still

around? Bluespec was supposed to by a player in the HLS field, but one has

to question their viability if they have given up on industry conferences.

- Cliff Cummings

Sunburst Design Provo, UT

---- ---- ---- ---- ---- ---- ----

|

Cliff Cummings has 24 years experience in RTL verification and synthesis training -- and is a founder of SystemVerilog and UVM.

He's won 15 SNUG "Best Papers Awards" out of 41 conference talks he's given since 1993. He looks older than this pic shows.

|

Related Articles:

Cliff Cummings verification-SystemVerilog-UVM DAC'16 Trip Report

Cliff Cummings verification-SystemVerilog-UVM DAC'15 Trip Report

Join

Index

Next->Item

|

|