( ESNUG 544 Item 3 ) -------------------------------------------- [11/14/14]

Subject: 750 engineer survey on HLS verification issues & power reduction

> This year's survey showed RTL power reduction techniques are balanced

> across guided/manual and automatic optimization. To that end, PowerPro

> utilizes deep sequential analysis -- originally developed in SLEC -- to

> look across 100's of registers to find the maximum power savings possible

> for *both* guided/manual and automated modes.

>

> - Shawn McCloud

> Calypto Design San Jose, CA

From: [ Mark Milligan of Calypto ]

Hi John,

Calypto just completed its 6th annual blind worldwide survey on High Level

Synthesis (HLS). 750 engineers and engineering managers responded.

Prior surveys were ESNUG 523 #5, 513 #4, 488 #4, 486 #7, and 479 #4.

---- ---- ---- ---- ---- ---- ----

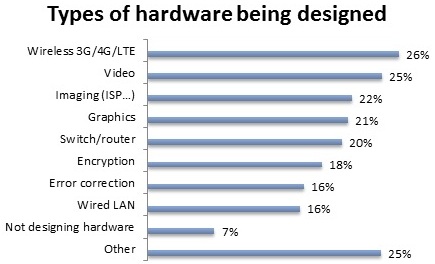

SURVEY DEMOGRAPHIC: TYPE OF HARDWARE BEING DESIGNED

Question 1: "What types of hardware are you designing?

Please pick ALL that apply."

The top designs where high level synthesis is most suitable were reflected

here. So far, the chip development teams that moved to HLS have:

- chips with complex algorithmic content

- chips where specs change quickly or standards evolve.

- and it's a race to get the chip into silicon quickly.

These design types are implemented faster with HLS vs. manually coding RTL.

---- ---- ---- ---- ---- ---- ----

IT'S ALL ABOUT SIMULATION SPEED

In addition, chips with massive verification requirements are also prime

to move to HLS. Functional C-level verification has 1,000x faster runtimes

as compared to Verilog or VHDL RTL runtimes.

Comparing for identical tests:

- Verilog or VHDL RTL simulation farm of 100 servers 10 hours

- C-level simulation on 1 server ~1 hour

Even using 99 LESS servers, C-level simulation is still 10X faster overall

than either Verilog or VHDL simulation!

Which gave us our next survey question on verification.

---- ---- ---- ---- ---- ---- ----

THE TOP ISSUES WITH HLS VERIFICATION FLOWS

Question 2: "What are your 2 biggest problems with your

High Level Synthesis verification flow?"

The top designs where high level synthesis is most suitable were reflected

here. So far, the chip development teams that moved to HLS have:

- chips with complex algorithmic content

- chips where specs change quickly or standards evolve.

- and it's a race to get the chip into silicon quickly.

These design types are implemented faster with HLS vs. manually coding RTL.

---- ---- ---- ---- ---- ---- ----

IT'S ALL ABOUT SIMULATION SPEED

In addition, chips with massive verification requirements are also prime

to move to HLS. Functional C-level verification has 1,000x faster runtimes

as compared to Verilog or VHDL RTL runtimes.

Comparing for identical tests:

- Verilog or VHDL RTL simulation farm of 100 servers 10 hours

- C-level simulation on 1 server ~1 hour

Even using 99 LESS servers, C-level simulation is still 10X faster overall

than either Verilog or VHDL simulation!

Which gave us our next survey question on verification.

---- ---- ---- ---- ---- ---- ----

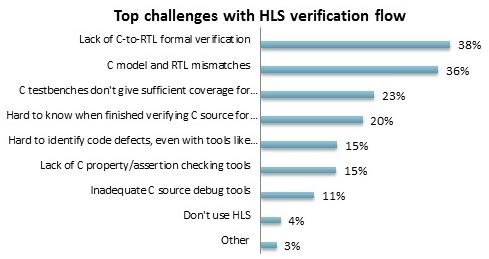

THE TOP ISSUES WITH HLS VERIFICATION FLOWS

Question 2: "What are your 2 biggest problems with your

High Level Synthesis verification flow?"

Moving to the C-level is a huge gain for functional verification and debug.

However, you can lose of some of this gain if you have issues with your HLS

verification flow. The top 3 hurdles that the engineers mentioned.

- C-TO-RTL FORMAL VERIFICATION (38%)

This is the need to formally prove the RTL output by your high

level synthesis tool is equivalent to its C-code source input.

Logical Equivalency Checking (LEC).

This is devilishly tough, because the resulting microarchitectures

can vary widely based on the HLS synthesis constraints. For

example, deeply pipelined or widely parallel architectures will

exhibit different sequential behavior, yet are the "same" from a

functional point of view.

This takes more than a strong sequential C-to-RTL formal LEC

verification tool - it also requires optimizing how your formal

LEC works with high level synthesis. To do it right, your LEC

must get appropriate guideposts as to design intent while also

remaining independence to ensure confidence in the LEC result.

Yet designers push for this because adding C-to-RTL formal LEC

to their flow can mean a dramatic reduction of the amount of

RTL regression simulation required.

- C MODEL AND RTL MISMATCHES (36%)

Respondents were concerned about how to track down mismatches

between final RTL and source C. This is likely due to perceived

concerns over working with machine generated Verilog or VHDL RTL;

and the fact that some HLS tools do not automatically generate

testbench sequences to track down when an issue does occur.

- INSUFFICIENT COVERAGE FOR RTL VERIFICATION (23%)

Adopting RTL verification methodologies like UVM can help ensure

high quality RTL. However, these methodologies have been developed

around an assumption that your RTL has been hand coded. So what

happens if the testbenches don't provide sufficient structural

coverage at the RTL?

---- ---- ---- ---- ---- ---- ----

WHERE POWER REDUCTION TOOLS/FEATURES ARE MOST WANTED

Question 3: "Where do you most want new tools/features

for POWER REDUCTION?"

Moving to the C-level is a huge gain for functional verification and debug.

However, you can lose of some of this gain if you have issues with your HLS

verification flow. The top 3 hurdles that the engineers mentioned.

- C-TO-RTL FORMAL VERIFICATION (38%)

This is the need to formally prove the RTL output by your high

level synthesis tool is equivalent to its C-code source input.

Logical Equivalency Checking (LEC).

This is devilishly tough, because the resulting microarchitectures

can vary widely based on the HLS synthesis constraints. For

example, deeply pipelined or widely parallel architectures will

exhibit different sequential behavior, yet are the "same" from a

functional point of view.

This takes more than a strong sequential C-to-RTL formal LEC

verification tool - it also requires optimizing how your formal

LEC works with high level synthesis. To do it right, your LEC

must get appropriate guideposts as to design intent while also

remaining independence to ensure confidence in the LEC result.

Yet designers push for this because adding C-to-RTL formal LEC

to their flow can mean a dramatic reduction of the amount of

RTL regression simulation required.

- C MODEL AND RTL MISMATCHES (36%)

Respondents were concerned about how to track down mismatches

between final RTL and source C. This is likely due to perceived

concerns over working with machine generated Verilog or VHDL RTL;

and the fact that some HLS tools do not automatically generate

testbench sequences to track down when an issue does occur.

- INSUFFICIENT COVERAGE FOR RTL VERIFICATION (23%)

Adopting RTL verification methodologies like UVM can help ensure

high quality RTL. However, these methodologies have been developed

around an assumption that your RTL has been hand coded. So what

happens if the testbenches don't provide sufficient structural

coverage at the RTL?

---- ---- ---- ---- ---- ---- ----

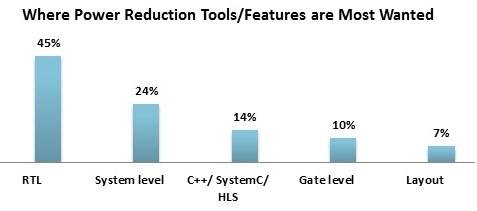

WHERE POWER REDUCTION TOOLS/FEATURES ARE MOST WANTED

Question 3: "Where do you most want new tools/features

for POWER REDUCTION?"

Power reduction at the Verilog/VHDL RTL level has been getting some press

lately because the higher you go up the level of abstraction, the more

opportunities there are for optimizing power. So moving beyond typical

gate and physical power techniques are clearly needed.

Yet there are additional power reductions to be had -- HLS can extend what

designers can do. It brings in low power microarchitecture exploration.

HLS can also capitalize on increasingly accurate RTL power estimation tools

to create power-, performance-, and area-optimized designs

Even so, only 1 in 7 respondents (14%) listed "more C++/SystemC/HLS power

reduction" as their top pick. I believe this will increase over time, as

HLS low power reduction advances -- and its results are demonstrated.

---- ---- ---- ---- ---- ---- ----

I want to add to this survey report that this year Calypto Catapult HLS

will be adding:

- Catapult HLS will now use design knowledge to create guaranteed

equivalent points -- which designers can use to match their

output Verilog/VHDL RTL structures to their relevant input C++

(or input SystemC) source code.

- Catapult HLS will now automatically create RTL testbenches based

on the input C++ or SystemC tests.

- Catapult HLS will now create verification-optimized RTL so that

the same vectors that cover the input C source will also cover

the output Verilog/VHDL RTL. This reduces the need to write new

coverage tests for Catapult-generated RTL. If the engineer does

identify any verification holes, Catapult now makes it easy to

navigate back to the HLS C source -- and to write new C++ or

SystemC tests.

We've made Catapult HLS act more like RTL logic synthesis. This allows

designers to control which regions of their design are optimized.

It also allows both "top down" and "bottom up" design, to make it easy

for designers to integrate RTL IP and synthesize their system around it.

We even use our PowerPro under-the-hood to do low power transformations

during RTL generation.

- Mark Milligan

Calypto Design San Jose, CA

Editor's Note: As far as I can tell, these 3 new parts to Catapult

that Mark is talking about is NOT on Calypto.com. This might be an

accidental scoop -- heard FIRST on DeepChip! Oops! Yea! - John

---- ---- ---- ---- ---- ---- ----

Related Articles

648 engineers surveyed on RTL Power Reduction and HLS techniques

744 engineers surveyed on what HLS integrations they want next

A survey of 1,133 engineers on HLS vs. manual RTL time savings

Power reduction at the Verilog/VHDL RTL level has been getting some press

lately because the higher you go up the level of abstraction, the more

opportunities there are for optimizing power. So moving beyond typical

gate and physical power techniques are clearly needed.

Yet there are additional power reductions to be had -- HLS can extend what

designers can do. It brings in low power microarchitecture exploration.

HLS can also capitalize on increasingly accurate RTL power estimation tools

to create power-, performance-, and area-optimized designs

Even so, only 1 in 7 respondents (14%) listed "more C++/SystemC/HLS power

reduction" as their top pick. I believe this will increase over time, as

HLS low power reduction advances -- and its results are demonstrated.

---- ---- ---- ---- ---- ---- ----

I want to add to this survey report that this year Calypto Catapult HLS

will be adding:

- Catapult HLS will now use design knowledge to create guaranteed

equivalent points -- which designers can use to match their

output Verilog/VHDL RTL structures to their relevant input C++

(or input SystemC) source code.

- Catapult HLS will now automatically create RTL testbenches based

on the input C++ or SystemC tests.

- Catapult HLS will now create verification-optimized RTL so that

the same vectors that cover the input C source will also cover

the output Verilog/VHDL RTL. This reduces the need to write new

coverage tests for Catapult-generated RTL. If the engineer does

identify any verification holes, Catapult now makes it easy to

navigate back to the HLS C source -- and to write new C++ or

SystemC tests.

We've made Catapult HLS act more like RTL logic synthesis. This allows

designers to control which regions of their design are optimized.

It also allows both "top down" and "bottom up" design, to make it easy

for designers to integrate RTL IP and synthesize their system around it.

We even use our PowerPro under-the-hood to do low power transformations

during RTL generation.

- Mark Milligan

Calypto Design San Jose, CA

Editor's Note: As far as I can tell, these 3 new parts to Catapult

that Mark is talking about is NOT on Calypto.com. This might be an

accidental scoop -- heard FIRST on DeepChip! Oops! Yea! - John

---- ---- ---- ---- ---- ---- ----

Related Articles

648 engineers surveyed on RTL Power Reduction and HLS techniques

744 engineers surveyed on what HLS integrations they want next

A survey of 1,133 engineers on HLS vs. manual RTL time savings

Join

Index

Next->Item

|

|