( ESNUG 541 Item 1 ) -------------------------------------------- [05/23/14]

Subject: Customer benchmark of Ansys/Apache RedHawk vs. Cadence Voltus

> We've been working with Cadence Voltus, their new unannounced cell-based

> static/dynamic digital power analysis tool that replaces their present

> Cadence EPS tool and directly competes against Apache/Ansys Redhawk.

>

> We looked at Redhawk a few years ago and decided to not use it because it

> couldn't handle our larger design sizes (over 200 M instances) but the

> newer Cadence EPS could.

>

> - from http://www.deepchip.com/items/0534-01.html

From: [ Mighty Mouse ]

Hi, John,

Please keep me anon as usual since I just want to share our benchmark

experience we had on power signoff tools a few months ago.

My team is responsible for the backend tool support and, often times, also

directly does the PnR and signoff for our tapeouts. We do 28 nm for mobile

devices, communications equipment, and servers. Our design sizes typically

run in the range of 75 M to 100 M instances with a lot of IP content such

as ARM cores and embedded memories.

We have used Apache's RedHawk for power signoff over the past few years.

Generally we are happy with it, but as our design sizes have grown and we're

starting to see RedHawk runtimes becoming a bottleneck in our final signoff

during tape out. Our runtimes have gone from 10's of hours to several days

or more. This causes some anxiety and uncertainty in our tapeout schedules.

So late last year, when we heard about Voltus and its 10X speed claims, we

invited Cadence to do a competitive eval to check it out on an ARM-core

processor. (Frankly speaking, I'm VERY, VERY skeptical of any 10X speed

up claim, more like CDNS marketing hype. They've made claims like this

before on EPS and other products, and fell short of our expectations. But

if we could even get 2X boost that would be worth consideration.)

---- ---- ---- ---- ---- ---- ----

Out test design was a TSMC 28 nm, 80 M inst low power mobile processor chip.

It has 60 power nets, many as power-gated switching nets. The design also

has more than several thousand embedded memories.

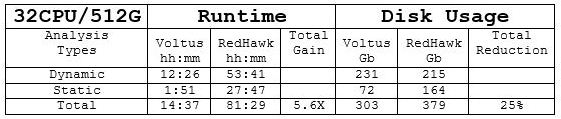

We wanted to run both static and dynamic power and IR-drop analysis on a

dedicated 32-CPU server with 512 G byte of memory.

Our main goal was to compare raw runtime numbers and disk space usages.

We liked that Voltus could cut this 3 1/2 day run into one *overnight* run.

This would let our engineers turn power signoff runs around daily.

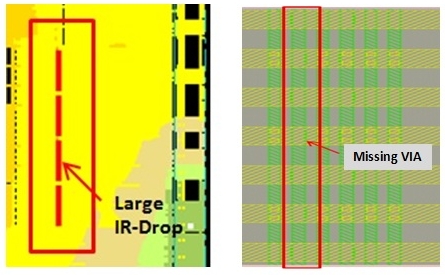

One surprise was Voltus found a weak spot in our power grid that RedHawk had

missed. It was due to missing vias on a piece of metal inside a large IP.

We liked that Voltus could cut this 3 1/2 day run into one *overnight* run.

This would let our engineers turn power signoff runs around daily.

One surprise was Voltus found a weak spot in our power grid that RedHawk had

missed. It was due to missing vias on a piece of metal inside a large IP.

Voltus IP's PGV modeling (Power-Grid-View) was able to draw a more accurate

tap current distribution and pinpoint this large IR-drop.

---- ---- ---- ---- ---- ---- ----

VOLTUS GOTCHAS

There were some drawbacks to Voltus that we'd like to see fixed:

1. Cadence claims a huge capability with Voltus' hierarchical analysis.

But we didn't run this because their AE told us that we don't have

to unless our designs are beyond 100 M to 150 M inst range.

2. We've asked Cadence integrate Voltus to their Sigrity package-board

analysis tool suite for chip-package-board co-simulation, as we

are moving down to TSMC 16 nm FinFET and 3D-IC. Cadence can not

replace Apache 100% until their co-simulation flow is also extended

to thermal analysis.

3. The Voltus GUI needs help.

4. Voltus IP lib PGV generation needs some simplification and better

throughput.

Despite these shortcomings, our conclusion in this eval is to switch from

RedHawk to Voltus. Going from 3.5 day RedHawk runs to overnight Voltus

runs is what decided it for our engineers.

- [ Mighty Mouse ]

Voltus IP's PGV modeling (Power-Grid-View) was able to draw a more accurate

tap current distribution and pinpoint this large IR-drop.

---- ---- ---- ---- ---- ---- ----

VOLTUS GOTCHAS

There were some drawbacks to Voltus that we'd like to see fixed:

1. Cadence claims a huge capability with Voltus' hierarchical analysis.

But we didn't run this because their AE told us that we don't have

to unless our designs are beyond 100 M to 150 M inst range.

2. We've asked Cadence integrate Voltus to their Sigrity package-board

analysis tool suite for chip-package-board co-simulation, as we

are moving down to TSMC 16 nm FinFET and 3D-IC. Cadence can not

replace Apache 100% until their co-simulation flow is also extended

to thermal analysis.

3. The Voltus GUI needs help.

4. Voltus IP lib PGV generation needs some simplification and better

throughput.

Despite these shortcomings, our conclusion in this eval is to switch from

RedHawk to Voltus. Going from 3.5 day RedHawk runs to overnight Voltus

runs is what decided it for our engineers.

- [ Mighty Mouse ]

Join

Index

Next->Item

|

|