( ESNUG 538 Item 7 ) -------------------------------------------- [04/04/14]

Subject: Why we switched from CDNS EDI/PT flow to MENT Olympus-SoC/PT flow

> From reader feedback, it appears the ICC II technical details my spies

> reported were very close, if not spot on. Aart's talk about "better

> throughput" and multi-CPU was clearly aimed at knocking down Atoptech.

>

> But, to be honest, my spies didn't predict the strong "floorplanning"

> spin SNPS put in the ICC II launch. On cue, Imagination/STmicro/LSI

> all gushed on how ICC II's super-fantabulous floorplanning sped their

> design process by 7X to 10X. That is, Aart is positioning ICC II to

> also attack Cadence EDI's First Encounter floorplanning franchise.

>

> - from http://www.deepchip.com/items/0538-01.html

From: [ The Lone Ranger ]

Hi, John,

Please keep me anonymous.

Good job on getting the scoop on ICC II so early before SNUG.

I can't speak about ICC use (because we're an ex-Cadence house), but I can

share why we switched from CDNS EDI to MENT Olympus-SoC.

---- ---- ---- ---- ---- ---- ----

FLOORPLANNING & PLACEMENT

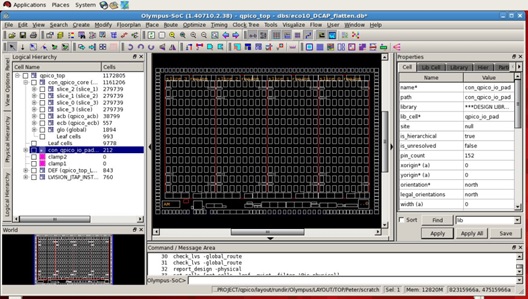

Without being too specific, we design TSMC 40/28 nm, 320 Mhz, 1 M inst chips

that are a sea of analog cells and memory macros (40%) with std cells (60%)

densely placed in between. When we used CDNS EDI, it couldn't uniformly

distribute the std cells to minimize congestion nor meet our IR-drop specs.

Old flow

1. Cadence RC Compler

2. Cadence EDI PnR

3. Cadence QRC extraction

4. Synopsys PrimeTime and PrimeTime-SI

5. Apache VoltageStorm

New flow

1. Synopsys Design Compiler

2. Mentor Olympus-SoC

3. Mentor Calibre XACT-SoC

4. Synopsys PrimeTime and PrimeTime-SI

5. Apache VoltageStorm

We did hierarchical floorplanning inside Olympus-SoC, bottom up, where we

partitioned our design into four different blocks. We pre-placed all the

analog ports on the blocks and then assembled at top level for closure.

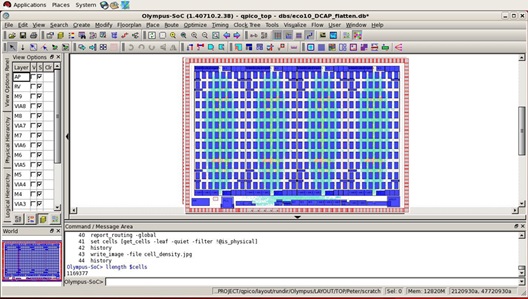

The initial Olympus-SoC placement got fairly good cell density. From what

we saw, it correlated well with the final congestion map after routing.

The initial Olympus-SoC placement got fairly good cell density. From what

we saw, it correlated well with the final congestion map after routing.

We were happy to see the placer effectively utilize the area between our

macros and spread the cells to minimize congestion and IR drop issues.

---- ---- ---- ---- ---- ---- ----

OPTIMIZATION

Our design had 8 MCMM scenarios that we had to optimize for both timing and

power. With CDNS EDI we had trouble converging on timing with our 8 corners

enabled, and it took almost 4 weeks with 20 ECO runs.

With Olympus we did all 8 corner simultaneously. It concurrently optimized

for timing, SI, and power across all 8 scenarios. We closed in 6 days with

7 ECO iterations.

Olympus-SoC> update_timing

info TA_CMDS6300: Running Multi-Core Timing Analysis using 6 CPUs.

warning TA_CMDS58: There is no enabled design mode for corner

'func_ss_tn40_v108_cw_setup'. Please disable it, otherwise

timing could be inaccurate.

warning TA_CMDS2503: Path group outputs does not exist. Can not modify.

warning TA_CMDS54: There is no max library defined for corner

'func_ss_tn40_v108_cw_setup'.

warning TA_CMDS55: There is no min library defined for corner

'func_ss_tn40_v108_cw_setup'.

info extr538: The corner func_ss_t125_v108_cw_setup check passed!

info extr538: The corner func_ss_t125_v108_cw_hold check passed!

info extr538: The corner func_ss_tn40_v108_rcw_setup check passed!

info extr538: The corner func_ss_tn40_v108_rcw_hold check passed!

info extr538: The corner func_ff_t0_v132_cb_setup check passed!

info extr538: The corner func_ff_t0_v132_cb_hold check passed!

info extr538: The corner func_ss_tn40_v108_cw_setup check passed!

info extr540: The Extraction Technology Check Passed!

info UI33: performed update timing for 41 minutes 28 seconds

(CPU time: 2 hours 46 minutes 0 seconds, current memory usage: 20387 M)

Olympus-SoC MCMM Variability Report

Olympus-SoC> report_var

info UI33: performed update timing for 0 seconds

(CPU time: 0 seconds, current memory usage: 20387 M)

------------------------------------------------------------------------

| MCMM variability report for design 'happy_top' (nano) |

|----------------------------------------------------------------------|

| | WNS TNS #Endpts WHS THS #Endpts |

|----------------------------------------------------------------------|

| **global** | -0.505 -300.6 2953 -0.813 -235.6 3891 |

| ss_t125_v108_cw_setup | -0.472 -126.8 1804 -ne- -ne- -ne- |

| ss_t125_v108_cw_hold | -ne- -ne- -ne- -0.785 -108.4 255 |

| ss_tn40_v108_rcw_setup | -0.505 -217.8 1599 -ne- -ne- -ne- |

| ss_tn40_v108_rcw_hold | -ne- -ne- -ne- -0.813 -103.8 265 |

| ff_t0_v132_cb_setup | 0.000 0.000 0 -ne- -ne- -ne- |

| ff_t0_v132_cb_hold | -ne- -ne- -ne- -0.533 -213.9 3891 |

------------------------------------------------------------------------

Since they're both MENT tools, we weren't surprised that Olympus-SoC numbers

correlated very well with Calibre XACT-SoC. It also correlated well with

PrimeTime and PrimeTime-SI.

---- ---- ---- ---- ---- ---- ----

ROUTING

Both the analog cells and memories (which took up 40% of our design) used

Metal1 through Metal4. Our power mesh also took up significant resources

due to our stringent IR-drop requirements. Our EDI flow had a lot of

congestion due to these limited routing resources and poor correlation

between the global and detailed routing engines. We had a higher number

of DRCs leading to longer ECO cycles.

The Olympus router closed using the available resources. Its GR-based

congestion estimates were consistent before and after routing. We used a

bottom up approach and routed our analog contacts first (Metal6-9) and

created a DEF file. Locked the analog contact route positions and used

the remaining space to route our std cell logic using Metal1 to Metal9.

---- ---- ---- ---- ---- ---- ----

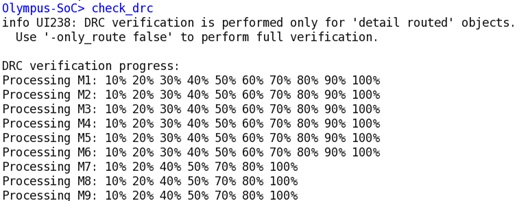

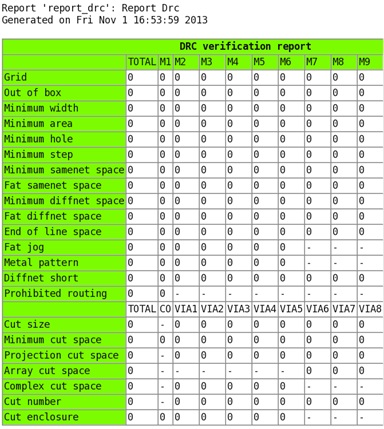

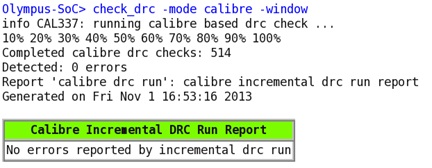

DRC/LVS/SIGN-OFF

Our EDI physical verification sign off cycle was painful due to multiple

iterations between EDI and PrimeTime to detect and fix DRC issues. This

was caused because of a miscorrelation between the outdated router

technology rule files and the SVRF deck used by the signoff tools.

We were happy to see the placer effectively utilize the area between our

macros and spread the cells to minimize congestion and IR drop issues.

---- ---- ---- ---- ---- ---- ----

OPTIMIZATION

Our design had 8 MCMM scenarios that we had to optimize for both timing and

power. With CDNS EDI we had trouble converging on timing with our 8 corners

enabled, and it took almost 4 weeks with 20 ECO runs.

With Olympus we did all 8 corner simultaneously. It concurrently optimized

for timing, SI, and power across all 8 scenarios. We closed in 6 days with

7 ECO iterations.

Olympus-SoC> update_timing

info TA_CMDS6300: Running Multi-Core Timing Analysis using 6 CPUs.

warning TA_CMDS58: There is no enabled design mode for corner

'func_ss_tn40_v108_cw_setup'. Please disable it, otherwise

timing could be inaccurate.

warning TA_CMDS2503: Path group outputs does not exist. Can not modify.

warning TA_CMDS54: There is no max library defined for corner

'func_ss_tn40_v108_cw_setup'.

warning TA_CMDS55: There is no min library defined for corner

'func_ss_tn40_v108_cw_setup'.

info extr538: The corner func_ss_t125_v108_cw_setup check passed!

info extr538: The corner func_ss_t125_v108_cw_hold check passed!

info extr538: The corner func_ss_tn40_v108_rcw_setup check passed!

info extr538: The corner func_ss_tn40_v108_rcw_hold check passed!

info extr538: The corner func_ff_t0_v132_cb_setup check passed!

info extr538: The corner func_ff_t0_v132_cb_hold check passed!

info extr538: The corner func_ss_tn40_v108_cw_setup check passed!

info extr540: The Extraction Technology Check Passed!

info UI33: performed update timing for 41 minutes 28 seconds

(CPU time: 2 hours 46 minutes 0 seconds, current memory usage: 20387 M)

Olympus-SoC MCMM Variability Report

Olympus-SoC> report_var

info UI33: performed update timing for 0 seconds

(CPU time: 0 seconds, current memory usage: 20387 M)

------------------------------------------------------------------------

| MCMM variability report for design 'happy_top' (nano) |

|----------------------------------------------------------------------|

| | WNS TNS #Endpts WHS THS #Endpts |

|----------------------------------------------------------------------|

| **global** | -0.505 -300.6 2953 -0.813 -235.6 3891 |

| ss_t125_v108_cw_setup | -0.472 -126.8 1804 -ne- -ne- -ne- |

| ss_t125_v108_cw_hold | -ne- -ne- -ne- -0.785 -108.4 255 |

| ss_tn40_v108_rcw_setup | -0.505 -217.8 1599 -ne- -ne- -ne- |

| ss_tn40_v108_rcw_hold | -ne- -ne- -ne- -0.813 -103.8 265 |

| ff_t0_v132_cb_setup | 0.000 0.000 0 -ne- -ne- -ne- |

| ff_t0_v132_cb_hold | -ne- -ne- -ne- -0.533 -213.9 3891 |

------------------------------------------------------------------------

Since they're both MENT tools, we weren't surprised that Olympus-SoC numbers

correlated very well with Calibre XACT-SoC. It also correlated well with

PrimeTime and PrimeTime-SI.

---- ---- ---- ---- ---- ---- ----

ROUTING

Both the analog cells and memories (which took up 40% of our design) used

Metal1 through Metal4. Our power mesh also took up significant resources

due to our stringent IR-drop requirements. Our EDI flow had a lot of

congestion due to these limited routing resources and poor correlation

between the global and detailed routing engines. We had a higher number

of DRCs leading to longer ECO cycles.

The Olympus router closed using the available resources. Its GR-based

congestion estimates were consistent before and after routing. We used a

bottom up approach and routed our analog contacts first (Metal6-9) and

created a DEF file. Locked the analog contact route positions and used

the remaining space to route our std cell logic using Metal1 to Metal9.

---- ---- ---- ---- ---- ---- ----

DRC/LVS/SIGN-OFF

Our EDI physical verification sign off cycle was painful due to multiple

iterations between EDI and PrimeTime to detect and fix DRC issues. This

was caused because of a miscorrelation between the outdated router

technology rule files and the SVRF deck used by the signoff tools.

With Olympus we used Calibre sign-off and SVRF decks directly inside P&R

with InRoute. Since these had 100% correlation, we essentially eliminated

our physical verification ECO cycle.

We strongly believe this tight integration between Olympus and Calibre will

help in our future projects, especially for smaller nodes.

---- ---- ---- ---- ---- ---- ----

MENT FIX THIS

- We found that the Olympus floorplanning usability and GUI to be

lagging behind and needs improvement. We were using the older

version of Olympus and were able to work around some of these

issues.

- We have been told the latest Olympus release has an enhanced

floorplanner. We hope it'll address our usability concerns.

Overall we were happy that Olympus closed our unique designs and it is the

plan of record for our upcoming projects. Needless to say we are happy with

the Olympus-SoC tool and the support MENT gives for it.

- [ The Lone Ranger ]

With Olympus we used Calibre sign-off and SVRF decks directly inside P&R

with InRoute. Since these had 100% correlation, we essentially eliminated

our physical verification ECO cycle.

We strongly believe this tight integration between Olympus and Calibre will

help in our future projects, especially for smaller nodes.

---- ---- ---- ---- ---- ---- ----

MENT FIX THIS

- We found that the Olympus floorplanning usability and GUI to be

lagging behind and needs improvement. We were using the older

version of Olympus and were able to work around some of these

issues.

- We have been told the latest Olympus release has an enhanced

floorplanner. We hope it'll address our usability concerns.

Overall we were happy that Olympus closed our unique designs and it is the

plan of record for our upcoming projects. Needless to say we are happy with

the Olympus-SoC tool and the support MENT gives for it.

- [ The Lone Ranger ]

Join

Index

Next->Item

|

|