( ESNUG 537 Item 7 ) -------------------------------------------- [03/14/14]

Subject: Amit's post-CDNS-vs.-BDA-lawsuit SPICE trends/predictions for 2014

> - With Synopsys annexing Magma FineSim through the recent acquisition,

> Synopsys will monopolize the Custom Digital/IO and Memory/Standard

> Cell Library territories. Synopsys will recapture their estimated

> $70 million/year in lost business to Magma, and with Magma's history

> of price cutting and commoditizing now eliminated, the overall market

> size for SPICE tools will increase. This definitely fortresses the

> former Synopsys franchise with its huge margins to counter the low to

> negative margins seen in its IP business.

>

> - FineSim customers will start seeing their Synopsys salespeople after

> the close in Q2 2012, who will tell them how their price is going up

> dramatically. I suspect there will be very little discounting

> considered by Synopsys.

>

> "Reader details how SNPS-LAVA dramatically raises SPICE prices"

> http://www.deepchip.com/items/0496-07.html

From: [ Amit Gupta of Solido Design ]

Hi John,

I thought your DeepChip readers would be interested in an update to the

SPICE Wars piece you published in ESNUG 496 #7 in December 2011. There've

been some new product announcements since then plus the recent Cadence/BDA

lawsuit has been settled.

---- ---- ---- ---- ---- ---- ----

FOUR BIG TRENDS

TREND #1: SMALLER NODES MEANS FEWER PLAYERS

Due to cost, there's been a major move for IDM's to use dedicated foundries

for the advanced nodes. Below is an IHS iSuppli snapshot of the current fab

providers per process node:

45/40 nm 32/28 nm 22/20 nm 16/14 nm

-------- -------- -------- --------

SMIC UMC TSMC TSMC

UMC TSMC GlobalFoundries GlobalFoundries

TSMC GlobalFoundries Intel Intel

GlobalFoundries STMicro Samsung Samsung

Renesas Intel

IBM Samsung

Fujitsu

Toshiba

STMicro

Intel

Samsung

Notice that at 45/40 nm there are 11 fabs. At 16/14 nm only 4 fabs.

The vast majority of SPICE simulation runs we presently see worldwide are

TSMC, Intel, GlobalFoundries and Samsung at 28, 22, 20, 16 and 14 nm. It

would not surprise me if Gary Smith reported that those four fabs accounted

for 95% or more of the world's 2013 SPICE license purchases.

---- ---- ---- ---- ---- ---- ----

TREND #2: 20/16/14 NM DESIGN STARTS ARE ACCELERATING

The move to 20/16/14 nm design is a result of major consumer drivers like

mobile electronics, the internet of things, cloud computing and augmented

reality. These consumer drivers demand semiconductor speed, connectivity,

reliability, battery life, form factor and cost.

For example, the TSMC 16 nm FinFETs vs their 28 nm gets 2X gate density,

38% speed improvement at same power, and 54% improved power saving at the

same speed.

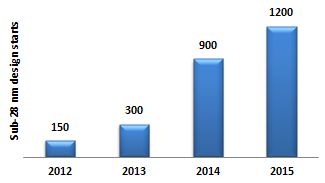

There were 150 sub-28 nm IC design starts in 2012, and 300 design starts in

2013. This is forecasted to grow to 1300 by 2015 -- with only 4 fabs left

making all of these chips.

---- ---- ---- ---- ---- ---- ----

TREND #3: NUMBER OF SPICE RUNS ARE INCREASING 10X to 1,000,000X

20/16/14 nm designs have far more potential failure regions than designers

have historically considered. Just for variation issues, we are seeing:

- PVT corner analysis: 100's-1,000's simulations

Designers must now cover all per-device type process, voltage,

temperature, load, parasitic RC conditions and corners caused

by double patterning lithography.

- 3-sigma design: 3000 simulations

Simulating the 1000's of Monte Carlo variation conditions using

the local and global statistical variation data provided in the

foundry PDK's.

- 4- to 6-sigma designs: millions to billions of simulations

It can take this infeasible number of Monte Carlo simulations to

fully cover conditions using the local and global variation data

provided in the foundry PDK's.

We see our customers' batch jobs executed using IBM Platform LSF, Oracle

Grid Engine or RTDA NetworkComputer cluster management software. We often

see clusters running 100's to 1000's of SPICE simulator licenses to

parallelize SPICE simulation runs to simulate various conditions and

perform PVT and Monte Carlo runs.

Designers of memory and std cell design continue to be the largest consumers

of SPICE simulation runs. Engineers are simulating their designs on each

new PDK revision from each foundry they use to eliminate any silicon failure

and overdesign penalty.

---- ---- ---- ---- ---- ---- ----

TREND #4: CONCERNED FOUNDRIES ARE PROVIDING RICHER SPICE PDK DECKS

When designing with 20/16/14 nm devices, variation is a first-order effect.

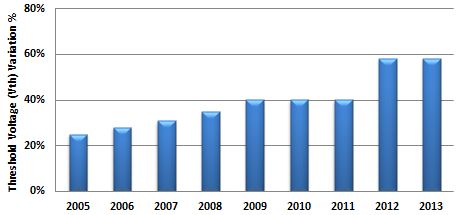

As shown by data from the ITRS, threshold voltage (Vth) variation increases

significantly with the scaling down to smaller process nodes.

There were 150 sub-28 nm IC design starts in 2012, and 300 design starts in

2013. This is forecasted to grow to 1300 by 2015 -- with only 4 fabs left

making all of these chips.

---- ---- ---- ---- ---- ---- ----

TREND #3: NUMBER OF SPICE RUNS ARE INCREASING 10X to 1,000,000X

20/16/14 nm designs have far more potential failure regions than designers

have historically considered. Just for variation issues, we are seeing:

- PVT corner analysis: 100's-1,000's simulations

Designers must now cover all per-device type process, voltage,

temperature, load, parasitic RC conditions and corners caused

by double patterning lithography.

- 3-sigma design: 3000 simulations

Simulating the 1000's of Monte Carlo variation conditions using

the local and global statistical variation data provided in the

foundry PDK's.

- 4- to 6-sigma designs: millions to billions of simulations

It can take this infeasible number of Monte Carlo simulations to

fully cover conditions using the local and global variation data

provided in the foundry PDK's.

We see our customers' batch jobs executed using IBM Platform LSF, Oracle

Grid Engine or RTDA NetworkComputer cluster management software. We often

see clusters running 100's to 1000's of SPICE simulator licenses to

parallelize SPICE simulation runs to simulate various conditions and

perform PVT and Monte Carlo runs.

Designers of memory and std cell design continue to be the largest consumers

of SPICE simulation runs. Engineers are simulating their designs on each

new PDK revision from each foundry they use to eliminate any silicon failure

and overdesign penalty.

---- ---- ---- ---- ---- ---- ----

TREND #4: CONCERNED FOUNDRIES ARE PROVIDING RICHER SPICE PDK DECKS

When designing with 20/16/14 nm devices, variation is a first-order effect.

As shown by data from the ITRS, threshold voltage (Vth) variation increases

significantly with the scaling down to smaller process nodes.

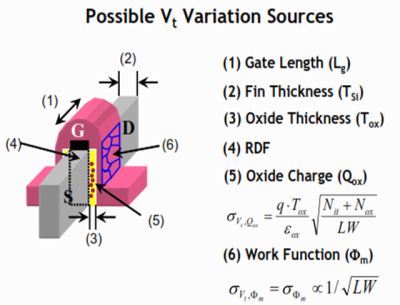

With 16 nm FinFET devices, the nature of variation changes. On planar CMOS,

random dopant fluctuations (RDFs) had the biggest influence.

With 16 nm FinFET devices, the nature of variation changes. On planar CMOS,

random dopant fluctuations (RDFs) had the biggest influence.

Ideal FinFETs have no doping, and therefore no RDFs. However, this only

works for low voltage operation. We also need high-speed devices, which

requires multiple threshold voltages (Vth's). For FinFETs, this requires

doping leading to RDF variation.

Furthermore, from Y. Liu at the VLSI Technology Symposium of 2010, there are

some new sources of variation such as gate lengths, fin thicknesses, oxide

thicknesses, etc. (shown in his figure above) that designers have to watch.

Because of this, TSMC, GlobalFoundries, Samsung and Intel are now providing

detailed statistical local (mismatch) and global manufacturing variation

data to 20/16/14 nm designers so they can hopefully get working silicon and

livable parametric yields -- without the designers having to over-design;

taking power, performance and area penalties.

Ideal FinFETs have no doping, and therefore no RDFs. However, this only

works for low voltage operation. We also need high-speed devices, which

requires multiple threshold voltages (Vth's). For FinFETs, this requires

doping leading to RDF variation.

Furthermore, from Y. Liu at the VLSI Technology Symposium of 2010, there are

some new sources of variation such as gate lengths, fin thicknesses, oxide

thicknesses, etc. (shown in his figure above) that designers have to watch.

Because of this, TSMC, GlobalFoundries, Samsung and Intel are now providing

detailed statistical local (mismatch) and global manufacturing variation

data to 20/16/14 nm designers so they can hopefully get working silicon and

livable parametric yields -- without the designers having to over-design;

taking power, performance and area penalties.

Why are TSMC, GlobalFoundries, Samsung and Intel doing this? It's due to

the terrible new economic costs their customers run into when they encounter

a "Black Swan Event" like a design respin. Since sub-28 nm design and

implementation costs are more than $100 million -- a single design respin

can cost over $10 million -- PLUS the lost TTM product revenue.

(FYI -- a "Black Swan Event" is an event that is seen as highly improbable

yet causes massive consequences. It comes from the belief that all swans

are white -- until an explorer discovered black swans in Australia. The

nature of "Black Swan Events" is that people AFTER THE FACT like Monday

Morning Quarterbacks like to say it must have been obvious that black swans

would have been found because other birds have color variations, too.)

---- ---- ---- ---- ---- ---- ----

RESULT: JIM HOGAN WAS RIGHT

November 2012, Jim Hogan predicted in ESNUG 515 #7, a Custom 2.0 retooling.

As a result of the trends above, I can confirm what Jim predicted. We have

been seeing an acceleration in SPICE retooling and investment for sub-28 nm

flows. Semiconductor company goals are:

- Differentiate by creating higher performance, lower power, smaller

area products.

- Accurately predict silicon performance for sub-28 nm design without

taking overdesign and yield/failure penalties

- Reduce design, respin costs and lost revenue

Below are typical problems we've seen from traditional SPICE simulation runs

that sub-28 nm SPICE simulation flow retooling addresses:

- PVT corner variation verification of 20 nm PLL took 2 weeks

- Verify 28 nm DAC non-linearity spec at 3-sigma took 1500 hours

- Verify 16 nm std cell library to 4-sigma took weeks to simulate,

and PVT corner simulation alone led to 15-30% overdesign

- Verify 14 nm SRAM memory design at 6-sigma took an infeasible

amount of time (years) to simulate, and linearity simplification

assumptions were not silicon-accurate

The result is not just increased retooling, but also a shift in the SPICE

simulation flow criteria. At larger nodes, designers were historically

able to get away with block-level simplifications -- including linear

approximations to estimate full-circuit performance. However, now these

simplifications are no longer possible.

Additional sub-28 nm complexity has placed increased demand on tool vendors

to deliver much higher performance / much higher capacity SPICE simulators

that are silicon-accurate. For example, simulating post-layout is a must;

as layout effects such as parasitics dramatically impact the power,

performance and silicon yield.

WHAT HOGAN MISSED:

One of the things we're seeing with customer retooling is that they've added

a new requirement above the traditional "more speed, more capacity, and more

accuracy" requests -- now we see customers also asking for increased design

coverage using fewers SPICE simulations.

Why are TSMC, GlobalFoundries, Samsung and Intel doing this? It's due to

the terrible new economic costs their customers run into when they encounter

a "Black Swan Event" like a design respin. Since sub-28 nm design and

implementation costs are more than $100 million -- a single design respin

can cost over $10 million -- PLUS the lost TTM product revenue.

(FYI -- a "Black Swan Event" is an event that is seen as highly improbable

yet causes massive consequences. It comes from the belief that all swans

are white -- until an explorer discovered black swans in Australia. The

nature of "Black Swan Events" is that people AFTER THE FACT like Monday

Morning Quarterbacks like to say it must have been obvious that black swans

would have been found because other birds have color variations, too.)

---- ---- ---- ---- ---- ---- ----

RESULT: JIM HOGAN WAS RIGHT

November 2012, Jim Hogan predicted in ESNUG 515 #7, a Custom 2.0 retooling.

As a result of the trends above, I can confirm what Jim predicted. We have

been seeing an acceleration in SPICE retooling and investment for sub-28 nm

flows. Semiconductor company goals are:

- Differentiate by creating higher performance, lower power, smaller

area products.

- Accurately predict silicon performance for sub-28 nm design without

taking overdesign and yield/failure penalties

- Reduce design, respin costs and lost revenue

Below are typical problems we've seen from traditional SPICE simulation runs

that sub-28 nm SPICE simulation flow retooling addresses:

- PVT corner variation verification of 20 nm PLL took 2 weeks

- Verify 28 nm DAC non-linearity spec at 3-sigma took 1500 hours

- Verify 16 nm std cell library to 4-sigma took weeks to simulate,

and PVT corner simulation alone led to 15-30% overdesign

- Verify 14 nm SRAM memory design at 6-sigma took an infeasible

amount of time (years) to simulate, and linearity simplification

assumptions were not silicon-accurate

The result is not just increased retooling, but also a shift in the SPICE

simulation flow criteria. At larger nodes, designers were historically

able to get away with block-level simplifications -- including linear

approximations to estimate full-circuit performance. However, now these

simplifications are no longer possible.

Additional sub-28 nm complexity has placed increased demand on tool vendors

to deliver much higher performance / much higher capacity SPICE simulators

that are silicon-accurate. For example, simulating post-layout is a must;

as layout effects such as parasitics dramatically impact the power,

performance and silicon yield.

WHAT HOGAN MISSED:

One of the things we're seeing with customer retooling is that they've added

a new requirement above the traditional "more speed, more capacity, and more

accuracy" requests -- now we see customers also asking for increased design

coverage using fewers SPICE simulations.

The reason why they're asking for this is because of the overall number of

SPICE simulations they have to run. For example, to characterize a 16 nm

SRAM cell can now easily take 5 billion SPICE runs.

Now the new SPICE retooling has 4 criteria instead of the usual 3 criteria

of "speed!, capacity!, accuracy!" by adding "more coverage in fewer sims!"

---- ---- ---- ---- ---- ---- ----

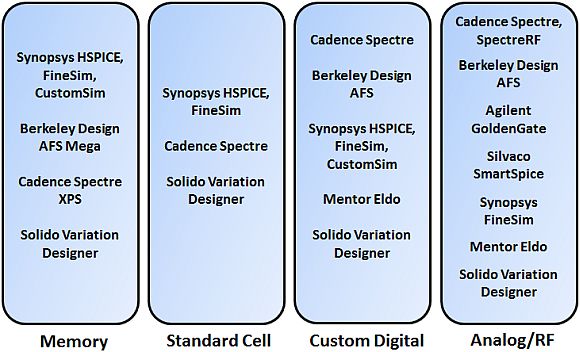

AMIT'S 2014 SPICE WARS UPDATE:

Let's take a look at the vendors in each of the four major SPICE segments:

The reason why they're asking for this is because of the overall number of

SPICE simulations they have to run. For example, to characterize a 16 nm

SRAM cell can now easily take 5 billion SPICE runs.

Now the new SPICE retooling has 4 criteria instead of the usual 3 criteria

of "speed!, capacity!, accuracy!" by adding "more coverage in fewer sims!"

---- ---- ---- ---- ---- ---- ----

AMIT'S 2014 SPICE WARS UPDATE:

Let's take a look at the vendors in each of the four major SPICE segments:

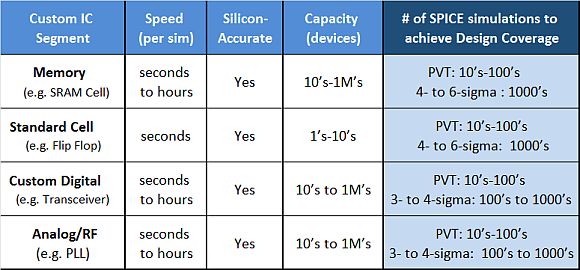

Each of these SPICE-use segments have different tool and use requirements.

Here's a breakout of each.

Memory

After Synopsys' acquisition of Magma in February 2012, Synopsys continues to

own the memory SPICE market (>80% market share) with their HSPICE, FineSim,

HSIM and CustomSim, -- from Avanti, Magma, Nassda, and their own R&D. They

have not merged any of these simulators as was originally speculated.

Some characteristics of memory designs include:

- Example designs are: bit cells, sense amps, columns, arrays

- Most design being done at leading process nodes (eg. 16/14 nm)

- Designers are running 10's-100's of SPICE simulator seats in

parallel to design, verify and characterize memory blocks

- Fabs running SPICE simulation on memory blocks to characterize

their processes and design IP for their customers

- Memory SPICE runs are done through command-line, not GUIs

- They use both true SPICE for high accuracy and Fast SPICE for

high capacity simulation

- Memory SPICE runs are often PVT and 3- to 6-sigma Monte Carlo

simulation for both design and verification

Both Cadence released their new Spectre XPS SPICE simulator and Berkeley DA

released their new AFS Mega simulator in 2013 -- in hopes to take this high

margin market niche from Synopsys. TSMC says it has adopted BDA AFS Mega.

Cadence so far has no announced major customer buy-ins of Spectre XPS.

Standard Cell

Synopsys also still dominates the standard cell SPICE simulation market with

more than 80% market share. The two major std cell SPICE simulators are

SNPS/Avanti HSPICE and SNPS/Magma FineSim. These two simulators dominate

because are tightly integrated into the Synopsys Liberty NCX and the market

dominant ex-Magma SiliconSmart standard cell characterization flows.

Some characteristics of std cell designs include:

- Example designs are: flip flops, inverters

- Most design being done at leading process nodes (eg. 16/14 nm)

- Designers are running 10's-100's of SPICE simulator seats in

parallel to design, verify and characterize std cell blocks

- Fabs running SPICE simulation on std cell blocks to design IP

libraries for their customers

- Std cell SPICE runs are done through command-line, not GUIs

- They use mosty true SPICE simulators for high accuracy, and

their runs are integrated with std cell characterization flows

- Std cell runs are often 4- to 6-sigma Monte Carlo simulation

for design and verification

Cadence bought Altos in 2011, actively hoping to capture some std cell SPICE

simulation market share for their Spectre with Virtuoso Liberate. We are

seeing CDNS/Altos Spectre getting some traction, i.e. it is being used more

by some customers for standard cell design.

Custom Digital

Cadence Spectre and Berkeley DA AFS (Analog FastSPICE) are the two major

simulators in the custom digital sub-market.

Some characteristics of custom digital designs include:

- Example designs are: SerDes, I/O's

- Design is being done at both older (eg. 45/28/22/20 nm) nodes

and leading process nodes (eg. 16/14 nm)

- Designers are running 1-10 SPICE simulator seats in parallel

to verify their custom designs

- Fabs don't usually do custom digital; their customers do it

- Custom digital SPICE runs are done through GUI's to setup and

launch simulations, and later visualize results

- They use both true SPICE simulators for high accuracy and

fast SPICE simulators for large capacity runs

- Custom digital runs are often PVT and 3- to 4-sigma Monte Carlo

Other vendors competing for this market share are Synopsys with HSPICE,

FineSim, CustomSim, and Mentor Eldo; but we mostly see Cadence Spectre

and Berkeley Design AFS simulators still dominating here.

Analog/RF

Cadence Spectre/Spectre RF and BDA Analog FastSPICE (AFS) are the two major

SPICE simulators for the analog/RF custom market. They continue to compete

aggressively.

Some characteristics of analog/RF designs include:

- Example designs are: OpAmps, PLLs, A/D or D/A converters

- Design is being done at both older (eg. 45/28/22/20 nm) nodes

and leading process nodes (eg. 16/14 nm)

- Designers are running 1-10 SPICE simulator seats in parallel

to verify their analog/RF designs

- Fabs don't usually do analog/RF; their customers do it

- Analog/RF SPICE runs are done through GUI's to setup and

launch simulations, and later visualize results

- They use both true SPICE simulators for high accuracy and

fast SPICE simulators for large capacity runs

- Analog/RF runs are often PVT and 3- to 4-sigma Monte Carlo

Other SPICE vendor simulators competing for market share in Analog/RF are

Synopsys FineSim (analog), Silvaco SmartSPICE (analog/RF), Mentor Eldo

(analog), Agilent GoldenGate (RF). We mostly see Cadence Spectre/SpectreRF

and Berkeley Design AFS used -- but with substantial Agilent GoldenGate

use for complex RF blocks.

---- ---- ---- ---- ---- ---- ----

AMIT'S SPICE PREDICTIONS FOR 2014:

Now that the CDNS/BDA lawsuit is settled and both companies' newly announced

SPICE simulators have had 6 months to harden, for 2014 I predict a shakeup in

the SPICE market:

- CDNS and BDA will chase after SNPS for the SPICE memory market

in 2014, and will announce customer wins since they have viable

product alternatives and customers want a second source supplier.

- CDNS will chase after SNPS for the SPICE std cell market in 2014,

and will announce customer wins with the Virtuoso Spectre/Altos

Liberate flow.

- CDNS and BDA will continue to battle for the SPICE custom digital

market in 2014, with BDA announcing more customer wins.

- BDA/Silvaco/Agilent/SNPS/MENT will chase after CDNS for the

SPICE analog/RF market in 2014. BDA, Silvaco and SNPS investment

will payoff in taking some market share from CDNS. Agilent and

MENT will stay status quo.

And I'm happy to say we are also seeing more SPICE variation simulation and

the need for coverage in fewer simulations, which clearly increase the need

for Solido tools -- but I might be biased on this. :)

- Amit Gupta

Solido DA Saskatoon, Canada

Each of these SPICE-use segments have different tool and use requirements.

Here's a breakout of each.

Memory

After Synopsys' acquisition of Magma in February 2012, Synopsys continues to

own the memory SPICE market (>80% market share) with their HSPICE, FineSim,

HSIM and CustomSim, -- from Avanti, Magma, Nassda, and their own R&D. They

have not merged any of these simulators as was originally speculated.

Some characteristics of memory designs include:

- Example designs are: bit cells, sense amps, columns, arrays

- Most design being done at leading process nodes (eg. 16/14 nm)

- Designers are running 10's-100's of SPICE simulator seats in

parallel to design, verify and characterize memory blocks

- Fabs running SPICE simulation on memory blocks to characterize

their processes and design IP for their customers

- Memory SPICE runs are done through command-line, not GUIs

- They use both true SPICE for high accuracy and Fast SPICE for

high capacity simulation

- Memory SPICE runs are often PVT and 3- to 6-sigma Monte Carlo

simulation for both design and verification

Both Cadence released their new Spectre XPS SPICE simulator and Berkeley DA

released their new AFS Mega simulator in 2013 -- in hopes to take this high

margin market niche from Synopsys. TSMC says it has adopted BDA AFS Mega.

Cadence so far has no announced major customer buy-ins of Spectre XPS.

Standard Cell

Synopsys also still dominates the standard cell SPICE simulation market with

more than 80% market share. The two major std cell SPICE simulators are

SNPS/Avanti HSPICE and SNPS/Magma FineSim. These two simulators dominate

because are tightly integrated into the Synopsys Liberty NCX and the market

dominant ex-Magma SiliconSmart standard cell characterization flows.

Some characteristics of std cell designs include:

- Example designs are: flip flops, inverters

- Most design being done at leading process nodes (eg. 16/14 nm)

- Designers are running 10's-100's of SPICE simulator seats in

parallel to design, verify and characterize std cell blocks

- Fabs running SPICE simulation on std cell blocks to design IP

libraries for their customers

- Std cell SPICE runs are done through command-line, not GUIs

- They use mosty true SPICE simulators for high accuracy, and

their runs are integrated with std cell characterization flows

- Std cell runs are often 4- to 6-sigma Monte Carlo simulation

for design and verification

Cadence bought Altos in 2011, actively hoping to capture some std cell SPICE

simulation market share for their Spectre with Virtuoso Liberate. We are

seeing CDNS/Altos Spectre getting some traction, i.e. it is being used more

by some customers for standard cell design.

Custom Digital

Cadence Spectre and Berkeley DA AFS (Analog FastSPICE) are the two major

simulators in the custom digital sub-market.

Some characteristics of custom digital designs include:

- Example designs are: SerDes, I/O's

- Design is being done at both older (eg. 45/28/22/20 nm) nodes

and leading process nodes (eg. 16/14 nm)

- Designers are running 1-10 SPICE simulator seats in parallel

to verify their custom designs

- Fabs don't usually do custom digital; their customers do it

- Custom digital SPICE runs are done through GUI's to setup and

launch simulations, and later visualize results

- They use both true SPICE simulators for high accuracy and

fast SPICE simulators for large capacity runs

- Custom digital runs are often PVT and 3- to 4-sigma Monte Carlo

Other vendors competing for this market share are Synopsys with HSPICE,

FineSim, CustomSim, and Mentor Eldo; but we mostly see Cadence Spectre

and Berkeley Design AFS simulators still dominating here.

Analog/RF

Cadence Spectre/Spectre RF and BDA Analog FastSPICE (AFS) are the two major

SPICE simulators for the analog/RF custom market. They continue to compete

aggressively.

Some characteristics of analog/RF designs include:

- Example designs are: OpAmps, PLLs, A/D or D/A converters

- Design is being done at both older (eg. 45/28/22/20 nm) nodes

and leading process nodes (eg. 16/14 nm)

- Designers are running 1-10 SPICE simulator seats in parallel

to verify their analog/RF designs

- Fabs don't usually do analog/RF; their customers do it

- Analog/RF SPICE runs are done through GUI's to setup and

launch simulations, and later visualize results

- They use both true SPICE simulators for high accuracy and

fast SPICE simulators for large capacity runs

- Analog/RF runs are often PVT and 3- to 4-sigma Monte Carlo

Other SPICE vendor simulators competing for market share in Analog/RF are

Synopsys FineSim (analog), Silvaco SmartSPICE (analog/RF), Mentor Eldo

(analog), Agilent GoldenGate (RF). We mostly see Cadence Spectre/SpectreRF

and Berkeley Design AFS used -- but with substantial Agilent GoldenGate

use for complex RF blocks.

---- ---- ---- ---- ---- ---- ----

AMIT'S SPICE PREDICTIONS FOR 2014:

Now that the CDNS/BDA lawsuit is settled and both companies' newly announced

SPICE simulators have had 6 months to harden, for 2014 I predict a shakeup in

the SPICE market:

- CDNS and BDA will chase after SNPS for the SPICE memory market

in 2014, and will announce customer wins since they have viable

product alternatives and customers want a second source supplier.

- CDNS will chase after SNPS for the SPICE std cell market in 2014,

and will announce customer wins with the Virtuoso Spectre/Altos

Liberate flow.

- CDNS and BDA will continue to battle for the SPICE custom digital

market in 2014, with BDA announcing more customer wins.

- BDA/Silvaco/Agilent/SNPS/MENT will chase after CDNS for the

SPICE analog/RF market in 2014. BDA, Silvaco and SNPS investment

will payoff in taking some market share from CDNS. Agilent and

MENT will stay status quo.

And I'm happy to say we are also seeing more SPICE variation simulation and

the need for coverage in fewer simulations, which clearly increase the need

for Solido tools -- but I might be biased on this. :)

- Amit Gupta

Solido DA Saskatoon, Canada

Join

Index

Next->Item

|

|