( ESNUG 531 Item 2 ) -------------------------------------------- [08/08/13]

Subject: SCOOP -- User benchmarks Celesda Vela as ~2X faster than Calibre

Editor's Note: Celesda's a new, unannounced DRC start-up! Their web

site is blank. All I could find was company founded in 2008; located

in Santa Clara and they gave a IEEE talk with this 2011 benchmark:

1 CPU 2 CPU 4 CPU 6 CPU

Chip 40 nm

9.2 GB 592 min 306 min 169 min 122 min

Which means Vela DRC scales well. Claims 30 tape-outs and can do TSMC

180 nm down to 28 nm. CEO is Haifang Liao, former Cadence SW architect

with 2 EDA patents. Beyond that Celesda's in stealth. Which means

this Vela DRC vs. Calibre benchmark is a SCOOP! Yea, baby! :) - John

---- ---- ---- ---- ---- ---- ----

From: [ Despicable Me 2 ]

Hi, John,

Please keep me and my company anonymous.

Our DRC runtimes are a headache for us, because we have 10 to 30 GB designs

that require lot of iterations.

After almost a full year eval, we bought Celesda Vela and have been using it

in production designs for DRC, metal fill, and DFM. As part of our eval, we

ran both Celesda Vela (v2012.01) and Mentor Calibre (v2012.4-25) on the same

designs using the same hardware. We then compared their speed and accuracy.

VELA DRC ACCURACY:

Vela's accuracy was the same as Calibre; technically even a bit higher than

Calibre. During our eval on 5 designs:

- Vela had no false errors, Vela had no missed errors.

- Calibre actually had one false error, but it was not

a significant issue.

In production use we haven't had one false error nor one missed error (so

far) with Celesda.

VELA DRC VS. CALIBRE DRC RUNTIMES:

Vela is *typically* about 1.6x-2.2x faster than Calibre on average. Vela

only took us only ~1 hour to set up for each new node. Input was either

GDSII or OASIS. Because we use multiple CPUs, I show both our total CPU

times and our actual human elapsed time.

Vela Calibre Vela Vela Calibre Vela

CPU CPU Speed Elapsed Elapsed Speed

Chip Time Time Up Time Time Up

-------- ---- ------- ------ ------- ------- -----

Chip A 317 min 598 min 1.9X 28 min 62 min 2.2X

(65 nm)

GDS: 3.2 GB

-----------------------------------------------------------------

Chip B 48 min 79 min 1.6X 6.6 min 9.7 min 1.5X

(45 nm)

GDS: 1.3 GB

-----------------------------------------------------------------

Chip C 1587 min 2754 min 1.7X 155 min 334 min 2.2x

(45 nm)

GDS: 10.9 GB

-----------------------------------------------------------------

Chip D 3663 min 4612 min 1.3X 322 min 613 min 1.9X

(45 nm)

GDS: 24.8 GB

-----------------------------------------------------------------

Chip E 3576 min 4441 min 1.2X 463 min 553 min 1.2X

(28nm)

GDS: 4.9 GB

-----------------------------------------------------------------

In general, we've found Vela beats Calibre by 2X or slightly better as the

design size grows.

The largest design we have run through Vela was a 6 GB OASIS file, which is

roughly equivalent to a 60 GB GDSII file. The design ran without issues,

though unfortunately I do not have the runtime data available to share.

That wall clock time 2X savings for each run adds up for us when we have a

lot of iterations to do.

VELA INTERFACE:

Vela's user interface is noticebly different from Calibre -- but it's so

self-explanatory that our designers used it right away without any training

from our CAD group. It's simple for them to load the results into our ADE

layout environment or Klayout and interpret the information.

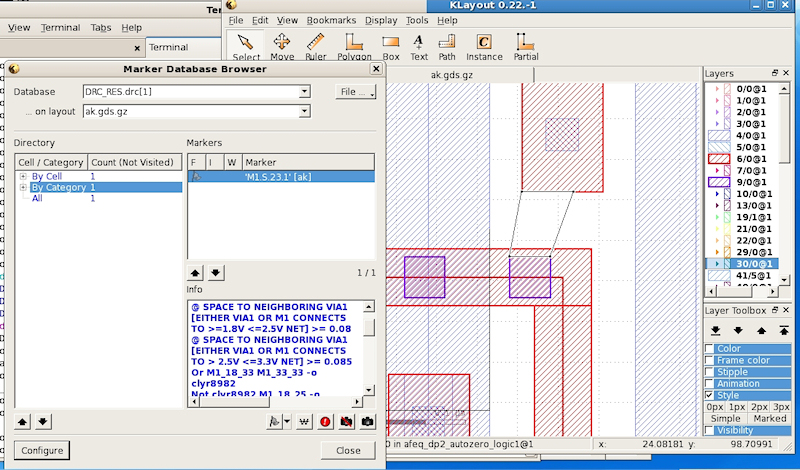

Fig 1. Vela connectivity-related spacing rule checking

(CLICK ON PIC TO ENLARGE IMAGE.)

Fig 1. Vela connectivity-related spacing rule checking

(CLICK ON PIC TO ENLARGE IMAGE.)

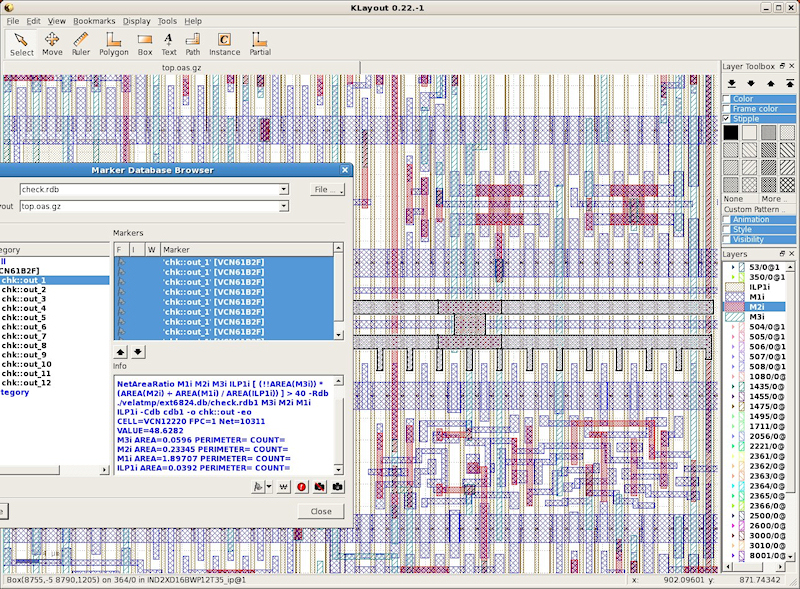

Fig 2. Vela antenna rule checking. The violated net is flagged.

(CLICK ON PIC TO ENLARGE IMAGE.)

We almost exclusively run Vela in batch mode because our typical designs are

so big. Vela has no GUI, but its output can be loaded into Klayout, which

is free with GNU license. (We like to use Klayout to minimize tying up

Virtuoso licenses just for a quick look at DRC results. Saves money.)

VELA HIERARCHICAL METAL FILL:

We use Vela for our metal fill -- it reads TSMC's foundry metafill utility,

then inserts the dummy fill into the GDSII.

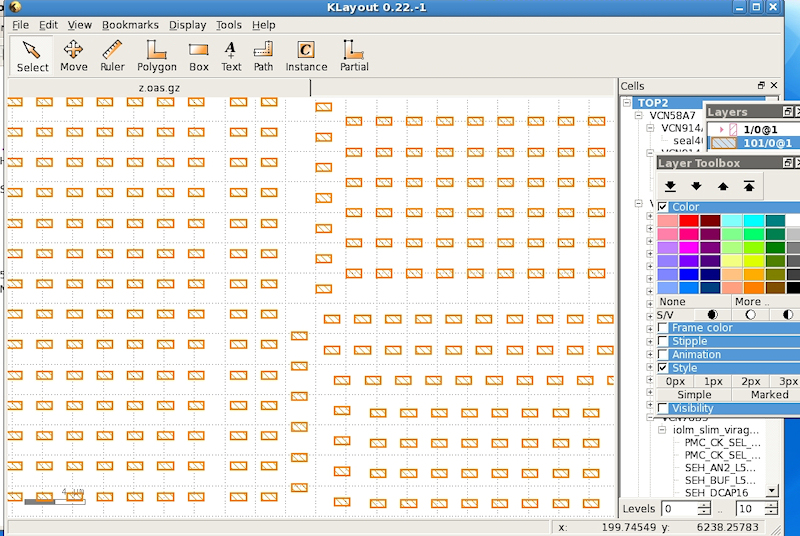

Vela can do hierarchical metal fill. As you can see in the example below,

the wide gap is on the cell boundary. It is small enough that no more metal

fill is needed.

Fig 2. Vela antenna rule checking. The violated net is flagged.

(CLICK ON PIC TO ENLARGE IMAGE.)

We almost exclusively run Vela in batch mode because our typical designs are

so big. Vela has no GUI, but its output can be loaded into Klayout, which

is free with GNU license. (We like to use Klayout to minimize tying up

Virtuoso licenses just for a quick look at DRC results. Saves money.)

VELA HIERARCHICAL METAL FILL:

We use Vela for our metal fill -- it reads TSMC's foundry metafill utility,

then inserts the dummy fill into the GDSII.

Vela can do hierarchical metal fill. As you can see in the example below,

the wide gap is on the cell boundary. It is small enough that no more metal

fill is needed.

Fig 3. Vela hierarchical metal fill output.

(CLICK ON PIC TO ENLARGE IMAGE.)

VELA DFM:

Two of the Celesda DFM features are very similar to Calibre YieldEnhancer's

"DFM Grow" and "DFM Property". However, Celesda does not require that you

purchase an extra license like Mentor does (e.g. with Mentor you have to buy

a separate license for Calibre YieldEnhancer).

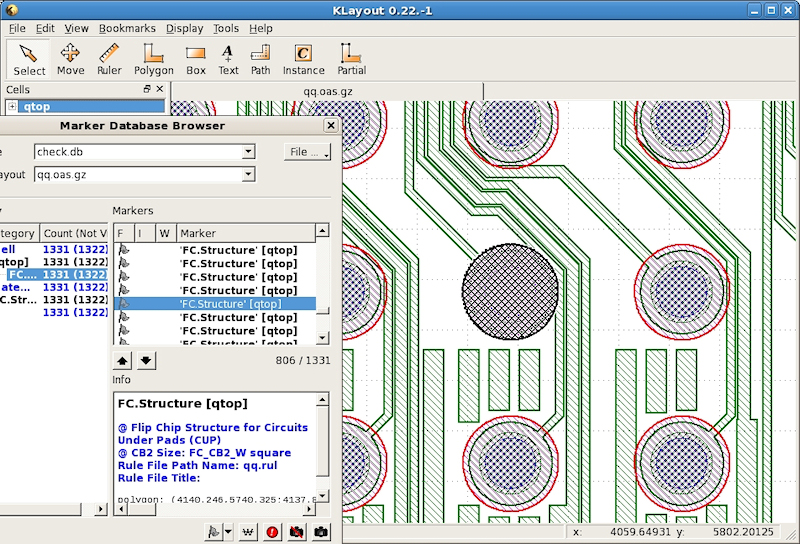

Below is an example of Vela's DFM property function, using equation-based

input.

Fig 3. Vela hierarchical metal fill output.

(CLICK ON PIC TO ENLARGE IMAGE.)

VELA DFM:

Two of the Celesda DFM features are very similar to Calibre YieldEnhancer's

"DFM Grow" and "DFM Property". However, Celesda does not require that you

purchase an extra license like Mentor does (e.g. with Mentor you have to buy

a separate license for Calibre YieldEnhancer).

Below is an example of Vela's DFM property function, using equation-based

input.

Fig 4. Vela equation-based DFM property function

(CLICK ON PIC TO ENLARGE IMAGE.)

Celesda told us they plan to support double patterning at 20 nm and below,

but we haven't seen it yet. We don't know if it's a tool issue or a PDK

availibility issue. Haven't asked.

CONCLUSION:

Celesda is now our default DRC tool for daily use by our team, because we

have a lot of time-consuming iterations during the design stage, and Vela

is faster than Calibre and can handle our big designs with faster than

Calibre can. However, our designers are free to use Calibre as they like,

as we have both tools.

Right now we still use Calibre for our final sign off.

We still have Calibre licenses, and sign-off only takes one run, so it still

makes sense to do this. Vela handles our daily routine DRC work without any

problem and our ultimate goal is to use Vela as a sign-off tool -- assuming

TSMC approves of it.

I'd definitely recommend Celesda. Calibre still has the monopoly in DRC,

but Celesda is bringing in good competition.

- [ Despicable Me 2 ]

Fig 4. Vela equation-based DFM property function

(CLICK ON PIC TO ENLARGE IMAGE.)

Celesda told us they plan to support double patterning at 20 nm and below,

but we haven't seen it yet. We don't know if it's a tool issue or a PDK

availibility issue. Haven't asked.

CONCLUSION:

Celesda is now our default DRC tool for daily use by our team, because we

have a lot of time-consuming iterations during the design stage, and Vela

is faster than Calibre and can handle our big designs with faster than

Calibre can. However, our designers are free to use Calibre as they like,

as we have both tools.

Right now we still use Calibre for our final sign off.

We still have Calibre licenses, and sign-off only takes one run, so it still

makes sense to do this. Vela handles our daily routine DRC work without any

problem and our ultimate goal is to use Vela as a sign-off tool -- assuming

TSMC approves of it.

I'd definitely recommend Celesda. Calibre still has the monopoly in DRC,

but Celesda is bringing in good competition.

- [ Despicable Me 2 ]

Join

Index

Next->Item

|

|