( ESNUG 524 Item 2 ) -------------------------------------------- [05/16/13]

Editor's Note: I got a hoot at how BDA has positioned their new ACE

by directly comparing it, point-by-point, to ADE's specific analog

characterization flaws. Wow. These BDA guys have no fear. - John

Subject: BDA tells CDNS "IN YOUR FACE" with new analog characterization

> USERS NOT HAPPY: In all the letters I've received on CDNS suing Berkeley,

> not one of them has taken a pro-Cadence stance. (Not one!) Yup, a lot of

> angry letters here, but those that stuck out the most had some fun, too.

>

> - from http://www.deepchip.com/items/0523-02.html

From: [ Paul "Pi" Estrada of BDA ]

Hi, John,

Although I'm sure the CDNS vs. BDA lawsuit story got you a lot of clicks on

DeepChip, I'd like to have your readers know that we're still very focused

on advancing EDA technology here.

To that point, today BDA has launched "ACE" our new Analog Characterization

Environment that enables analog designers to easily, quickly, and thoroughly

characterize SPICE circuits.

A THREEWAY CHOICE

ACE is an alternative to the two most common ways to characterize analog

circuits today, both of which are so difficult and time consuming that

analog designers are knowingly under-characterizing their circuits:

- Linux Command Line: This is the old school way. Analog

designers start with a SPICE netlist from a schematic

editor or some other means (e.g., a compiler, and then

manually edit it to specify the required circuit simulation

analyses and characterization variants (e.g., corners,

sweeps, and/or Monte Carlo). They launch their circuit

simulator (e.g., AFS, HSPICE, Spectre, FineSim) from the

UNIX command line specifying the modified netlist to run.

After simulation they may run a post-processing tool to

compute figures of merit based on the simulation outputs.

They may also write scripts that automate netlist

modifications, circuit simulator runs, and post-processing.

- Cadence Virtuoso ADE-XL: These analog designers always stay

within the Cadence Analog Design Environment (ADE). Assuming

they have ADE version 6.1, they use ADE-L to design and to

perform basic performance verification. They do sweeps

within ADE-L, but have to use ADE-XL for corners and Monte

Carlo. Many designers find ADE-L/-XL confusing, difficult to

use, and inefficient for characterization. Anything complex

requires extensive proprietary Cadence OCEAN scripting.

- BDA ACE: ACE provides an intuitive user interface to rapidly

set-up, launch, monitor, report, and visually analyze complex

analog characterization runs. ACE reduces hours of set-up

to just seconds. It also includes a powerful distribution

analyzer that makes it easy for designers to understand how

their circuits will perform in silicon. ACE can be run from

the command-line, ADE 5.1, or ADE-L 6.1. It supports leading

SPICE-compatible simulators and standard measure formats.

Lastly it includes an Open Verification Database for easy

flow integration and 3rd-party extensions.

The table below compares these three approaches. The ADE-XL information is

based on our understanding of that tool's capabilities. The rest of this

article explains the differences.

|

|

UNIX

Command-Line

|

Cadence

ADE-XL

|

BDA ACE

|

|

Variants

|

Corners, Sweeps,

and MC

|

Change

netlist

|

Inconsistent for

each type

|

Consistent for

all types

|

Nested

Combinations

|

Very limited

|

Limited

|

Extensive

|

|

Nest Set-up

|

Script (any)

|

Script (OCEAN)

|

Drag-&-drop

|

|

Nest Set-up Time

|

Hours

|

Hours

|

Seconds

|

Nest Post-

processing

|

None

|

Limited nests

|

Extensive nests

|

|

Multiple Tests

|

|

Set-up

|

No

|

Yes

|

Yes

|

|

Launch

|

No

|

Yes

|

Yes

|

|

Monitor

|

No

|

No

|

Yes

|

|

Measures

|

|

.measures

|

Yes

|

No

|

Yes

|

|

ADE measures

|

Yes

|

Yes

|

Yes

|

|

BDA Measures

|

Yes

|

No

|

Yes

|

|

Specifications

|

|

Min/max

|

No

|

Yes

|

Yes

|

|

Waveform

|

No

|

Yes, difficult

|

Yes, easy

|

|

2D

|

No

|

Yes, difficult

|

Yes, easy

|

Spec Pass/

Fail Report

|

No

|

Yes

|

Yes

|

|

Distribution Analysis

|

Histograms w/

Gaussian

|

No

|

Yes

|

Yes

|

|

Scatter Plots

|

No

|

Yes

|

Yes

|

Stacked

Histograms

|

No

|

No

|

Yes (with cross-

probing)

|

|

Mixed Data Sets

|

No

|

No

|

Yes (all nests)

|

|

Data Set Filtering

|

No

|

Unclear

|

Yes

|

Confidence

Interval

|

No

|

Unclear

|

Yes

(any conf. level)

|

|

Worst-case Yield

|

No

|

Unclear

|

Yes (binomial

conf. interval)

|

MC Iteration

Probability

|

No

|

No

|

Yes (patent

pending w/AFS)

|

|

Runtime

|

|

Simulators

|

AFS, HSPICE,

Spectre

|

AFS, HSPICE,

Spectre

|

AFS, HSPICE,

Spectre (Q3)

|

|

Runtime Per Core

|

5x-10x faster

with AFS

|

5x-10x faster

with AFS

|

5x-10x faster

with AFS

|

Max License

Efficiency

|

3x-4x with AFS

MCP

|

3x-4x with AFS

MCP - MC only

|

3x-4x with AFS

MCP

|

|

Data

|

Limited, unorganized

|

Limited access

via ADE

|

Unlimited

Open Verification

Database (OVD)

|

|

Environment

|

|

Command line

|

Yes

|

No

|

Yes

|

|

ADE 5.1

|

No

|

No

|

Yes

|

|

ADE-L 6.1

|

No

|

Yes

|

Yes

|

|

Scripting

|

Any

|

OCEAN

|

Any |

|

Run Scripts

|

No

|

Auto-generated,

limited nests

|

Auto-generated,

extensive nests

|

Third-Party

Extensibility

|

Yes, but no structure

|

Limited

|

Yes,

directly via OVD

|

VARIANTS

Characterization is about running VARIANTS of circuit TESTS and analyzing

the MEASUREMENT results of signals of interest. Variants, tests, and

measures are the building blocks.

Variants: The basic variants are corners, sweeps, and Monte Carlo. Unlike

ADE-XL in which each of these is specified in a completely different and

unrelated way, within ACE setting up corners, sweeps, and Monte Carlo is

consistent across all variant types. This is a big deal, because if it's

not obvious how to do something many designers quickly move on to other

tasks and those variants are unlikely to ever get covered. If designers

already have corners defined in ADE(-XL) or their PDK, ACE uses either

or both as-is.

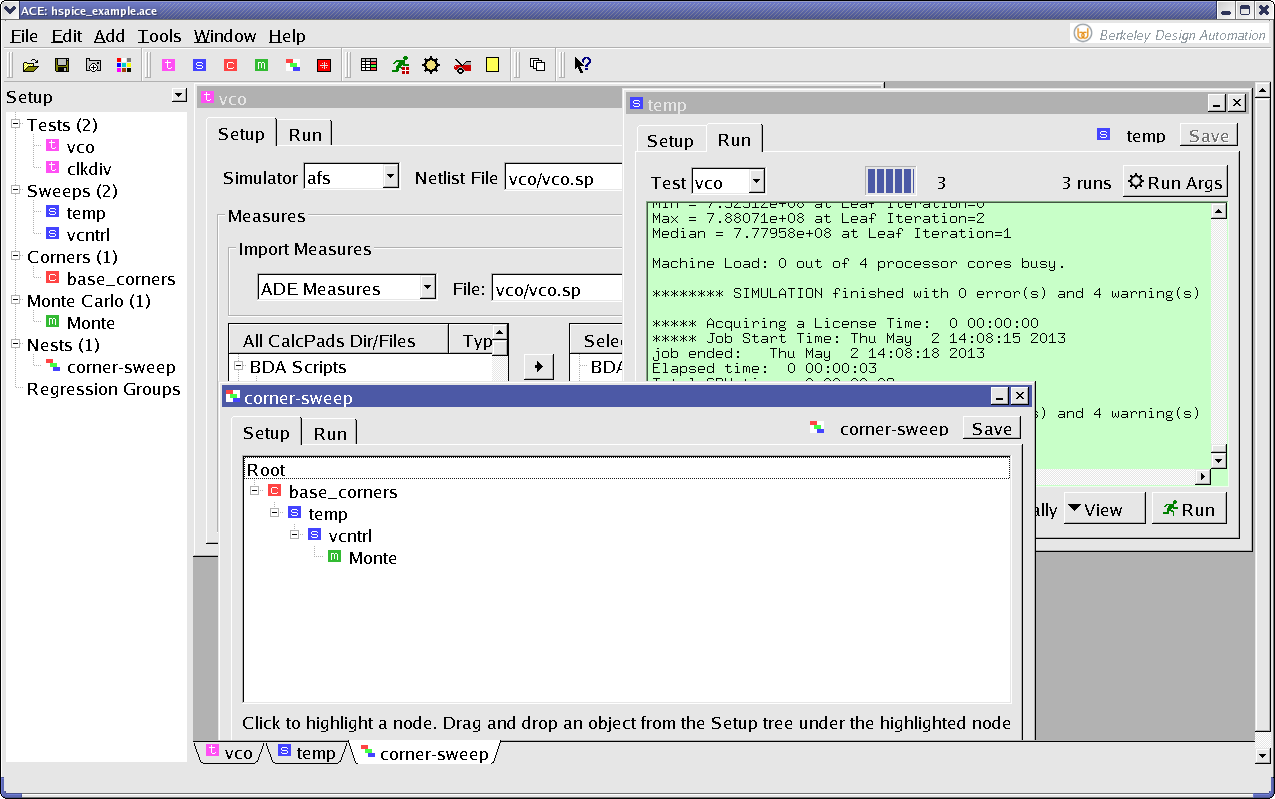

ACE users drag-and-drop corners, sweeps, and Monte Carlo variants to create

nests; including combinations that are not possible in HSPICE or via ADE-XL.

This is so easy that anyone who can use a mouse can do it. To get a

Corner > Sweep > Sweep > Monte Carlo

nest, just drag the corner into the nest window, drag the first sweep under

the corner, drag the second sweep under the first, and drag the Monte Carlo

under the second sweep. Done. It takes about as long as it took to read

that description. Try doing that in ADE-XL or from a command line. With

ACE it takes literally seconds to specify nests that would otherwise require

hours of writing and debugging scripts. ACE also automatically post-

processes all supported combinations; avoiding more, even worse scripting.

Tests: ACE uses the nominal tests that designers created during design. In

the Cadence world these are in ADE(-L) and in the Synopsys world they are

in a directory. ACE uses either or both as-is. Applying a variant to a

test is a simple drag-and-drop operation. (We tested the ease-of-use by

having an undergraduate EE student set-up a number of variants including

complex nests without any documentation or training. He had no problems.)

ACE users drag-and-drop corners, sweeps, and Monte Carlo variants to create

nests; including combinations that are not possible in HSPICE or via ADE-XL.

This is so easy that anyone who can use a mouse can do it. To get a

Corner > Sweep > Sweep > Monte Carlo

nest, just drag the corner into the nest window, drag the first sweep under

the corner, drag the second sweep under the first, and drag the Monte Carlo

under the second sweep. Done. It takes about as long as it took to read

that description. Try doing that in ADE-XL or from a command line. With

ACE it takes literally seconds to specify nests that would otherwise require

hours of writing and debugging scripts. ACE also automatically post-

processes all supported combinations; avoiding more, even worse scripting.

Tests: ACE uses the nominal tests that designers created during design. In

the Cadence world these are in ADE(-L) and in the Synopsys world they are

in a directory. ACE uses either or both as-is. Applying a variant to a

test is a simple drag-and-drop operation. (We tested the ease-of-use by

having an undergraduate EE student set-up a number of variants including

complex nests without any documentation or training. He had no problems.)

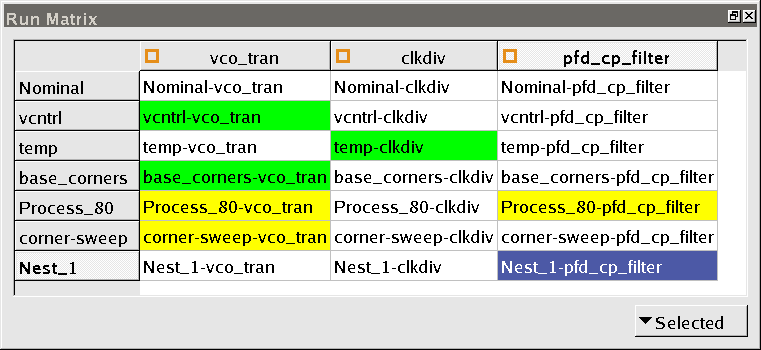

ACE includes a run matrix for defining which variants to run on which tests.

It's obvious how to select those to run (e.g., all, rows, columns, cells,

or "cherry pick"). ADE-XL has similar functionality. However, ACE takes

it a step further and uses the run matrix as a monitor at runtime. Color

coding indicates the cells that are in the queue, running, failed during

simulation, and ran to completion.

Measures: ACE also uses the measures that designers created during design.

Within Cadence ADE these are ADE measures and for Synopsys simulators they

are .measures. Again, ACE uses either or both as-is. ACE also includes

its own measures, a sophisticated calculator, and an extensive set of

pre-defined computations for figures-of-merit like SNR, jitter, or phase

noise.

SPECIFICATIONS

Within ACE designers specify pass/fail criteria for any of their measures

(e.g., minimum and/or maximum values). Designers often find it difficult

to specify all pass/fail criteria as scalar values. For such cases ACE

supports waveform and 2D specifications which apply to time-based and

frequency-based outputs. With ACE waveform specifications, a designer can

specify an existing waveform as a "golden" reference and specify a failure

as any results outside a min/max tolerance band relative to that waveform.

This is a good way to detect unanticipated problems. 2D specifications

allow designers to specify a piece-wise-linear pass/fail envelope, e.g., as

a phase noise specification. ADE-XL supports similar functionality, but it

is difficult to find and use.

ACE includes a run matrix for defining which variants to run on which tests.

It's obvious how to select those to run (e.g., all, rows, columns, cells,

or "cherry pick"). ADE-XL has similar functionality. However, ACE takes

it a step further and uses the run matrix as a monitor at runtime. Color

coding indicates the cells that are in the queue, running, failed during

simulation, and ran to completion.

Measures: ACE also uses the measures that designers created during design.

Within Cadence ADE these are ADE measures and for Synopsys simulators they

are .measures. Again, ACE uses either or both as-is. ACE also includes

its own measures, a sophisticated calculator, and an extensive set of

pre-defined computations for figures-of-merit like SNR, jitter, or phase

noise.

SPECIFICATIONS

Within ACE designers specify pass/fail criteria for any of their measures

(e.g., minimum and/or maximum values). Designers often find it difficult

to specify all pass/fail criteria as scalar values. For such cases ACE

supports waveform and 2D specifications which apply to time-based and

frequency-based outputs. With ACE waveform specifications, a designer can

specify an existing waveform as a "golden" reference and specify a failure

as any results outside a min/max tolerance band relative to that waveform.

This is a good way to detect unanticipated problems. 2D specifications

allow designers to specify a piece-wise-linear pass/fail envelope, e.g., as

a phase noise specification. ADE-XL supports similar functionality, but it

is difficult to find and use.

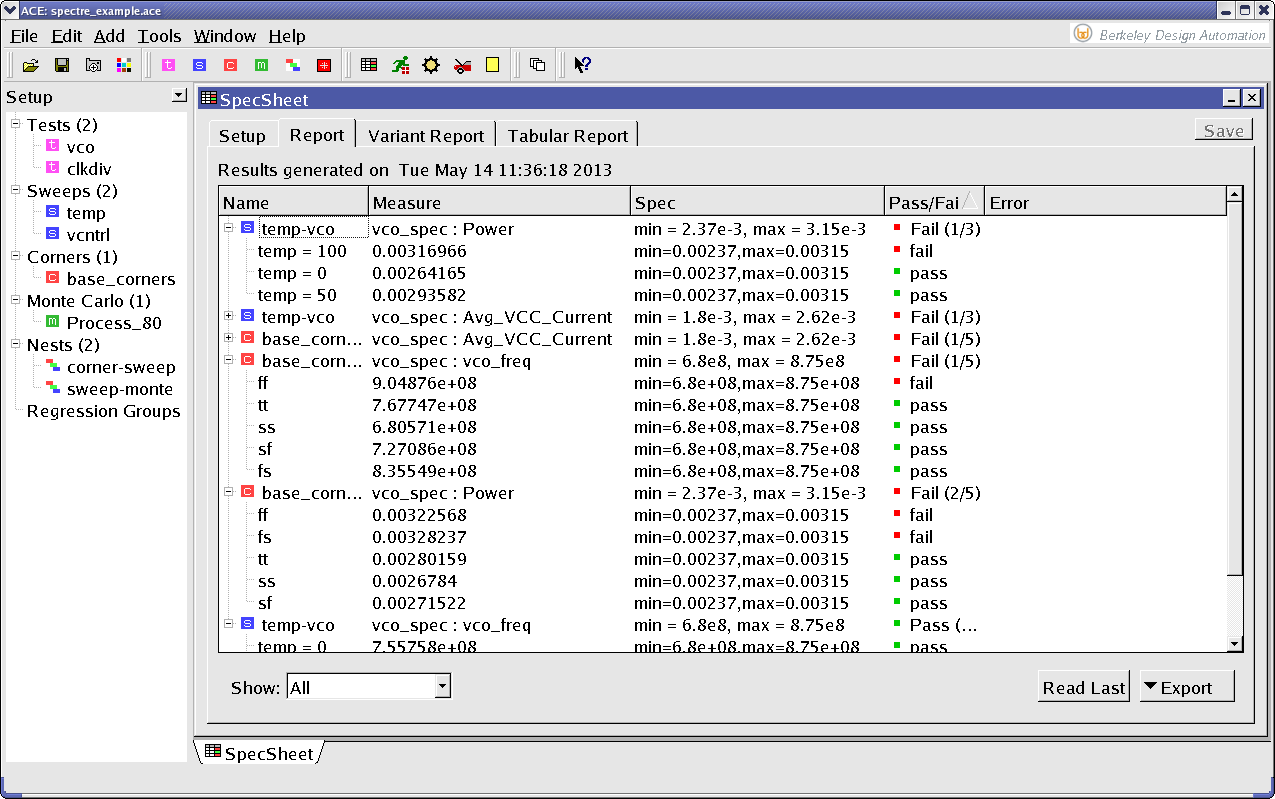

For every run, ACE generates a pass/fail "SpecSheet" report for every

measurement. This is a hierarchical report by test-variant combination

(i.e., Run Matrix cell). Users can export the contents of this in a CSV

or HTML format. This is pretty basic stuff, but it's automatic and saves

hours of tedious data collection, collation, and documentation (e.g. for

design reviews).

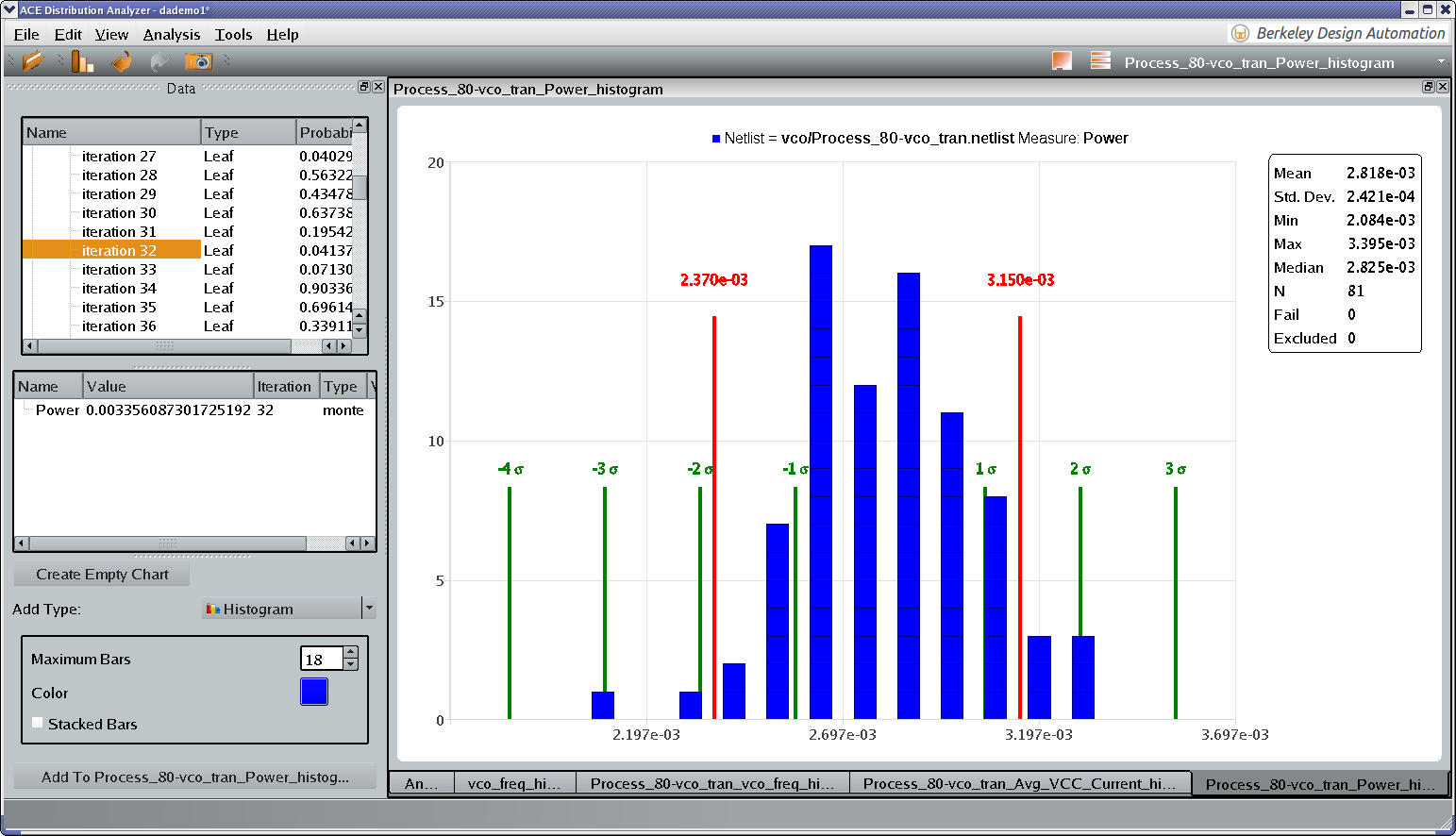

DISTRIBUTION ANALYSIS

Understanding how circuits will perform in silicon requires effective

characterization data mining, which the ACE Distribution Analyzer uniquely

provides.

For every run, ACE generates a pass/fail "SpecSheet" report for every

measurement. This is a hierarchical report by test-variant combination

(i.e., Run Matrix cell). Users can export the contents of this in a CSV

or HTML format. This is pretty basic stuff, but it's automatic and saves

hours of tedious data collection, collation, and documentation (e.g. for

design reviews).

DISTRIBUTION ANALYSIS

Understanding how circuits will perform in silicon requires effective

characterization data mining, which the ACE Distribution Analyzer uniquely

provides.

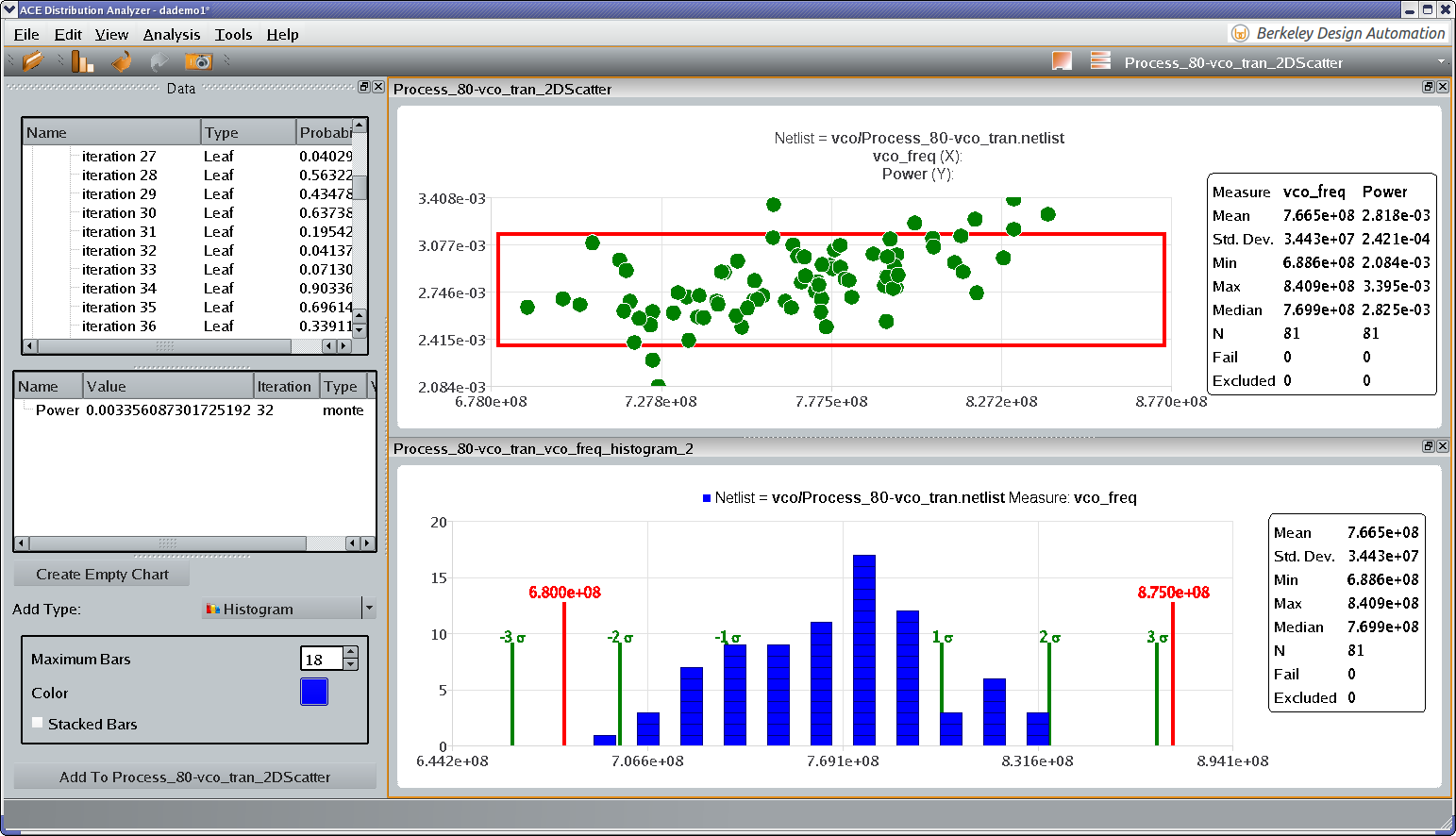

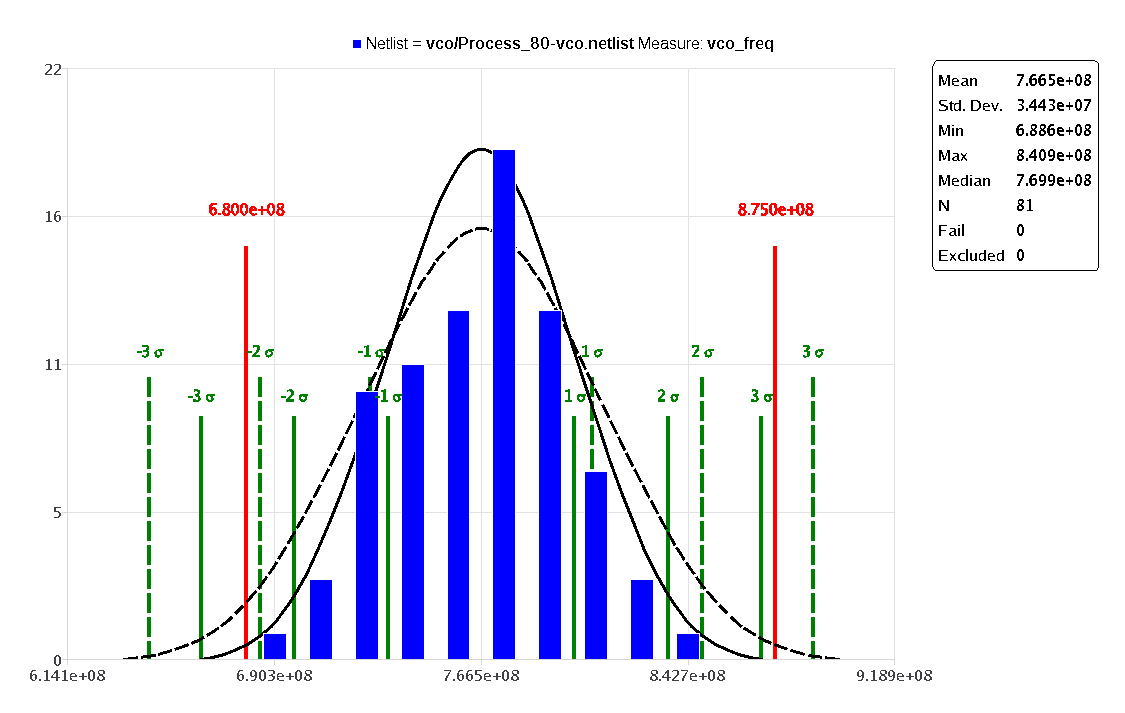

The ACE Distribution Analyzer enables designers to plot and analyze their

characterization results in seconds. At a glance designers can see

histogram-based distributions relative to any measure or set of measures;

and their associated specifications. Designers can overlay a Gaussian

curve. They can compare corner, sweep, and Monte Carlo results on the same

plots. They can exclude anomalous Monte Carlo iterations. They can

generate scatter plots. All of this visualization enables designers to

intuitively mine their data.

The ACE Distribution Analyzer enables designers to plot and analyze their

characterization results in seconds. At a glance designers can see

histogram-based distributions relative to any measure or set of measures;

and their associated specifications. Designers can overlay a Gaussian

curve. They can compare corner, sweep, and Monte Carlo results on the same

plots. They can exclude anomalous Monte Carlo iterations. They can

generate scatter plots. All of this visualization enables designers to

intuitively mine their data.

For yield analysis, ACE optionally displays the worst-case confidence-

interval impact in the Gaussian overlay and/or the sigma markers. At a

glance, designers know where their variants and specifications fall

relative to the sigma markers. By default ACE bases these computations

on a 95% confidence level, but users can change that default. For non-

Gaussian distributions, ACE includes a binomial confidence-interval

computation which provides the statistically relevant worst-case expected

yield for a given pass/fail data set.

For yield analysis, ACE optionally displays the worst-case confidence-

interval impact in the Gaussian overlay and/or the sigma markers. At a

glance, designers know where their variants and specifications fall

relative to the sigma markers. By default ACE bases these computations

on a 95% confidence level, but users can change that default. For non-

Gaussian distributions, ACE includes a binomial confidence-interval

computation which provides the statistically relevant worst-case expected

yield for a given pass/fail data set.

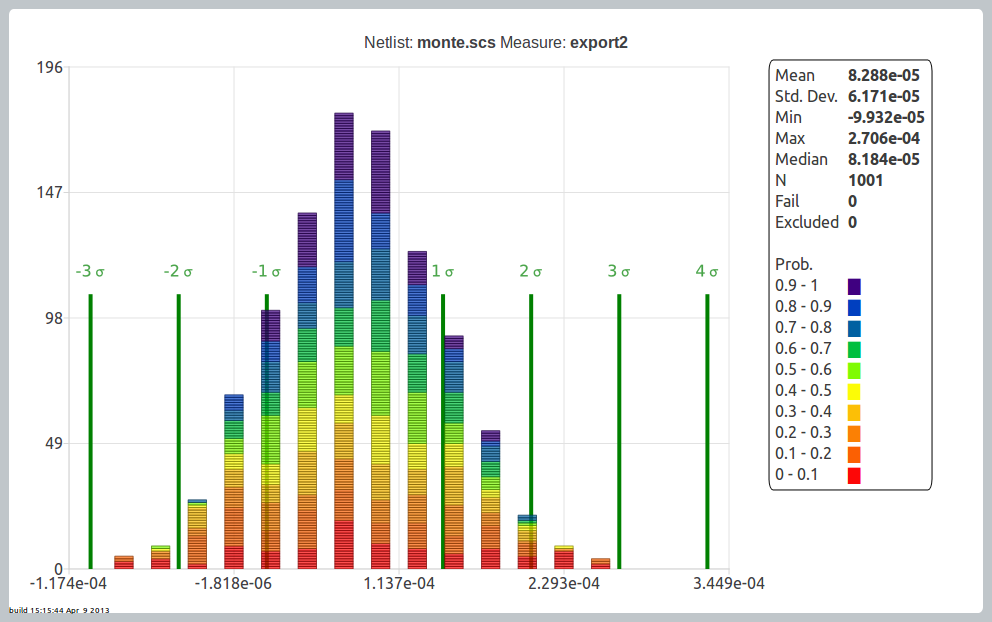

Last, ACE uniquely displays Monte Carlo iteration probabilities, i.e., the

likelihood that a given Monte Carlo iteration will occur relative to all

other possible iterations. Traditional Monte Carlo simulation does not

compute iteration probabilities, so designers assume that each iteration

has an equal weighting. An iteration at 3 sigma is just that -- an iteration

at 3 sigma. However, an iteration that is more likely than 50% of possible

iterations is clearly much more important than one that is more likely than

just 0.01% of possible iterations.

Last, ACE uniquely displays Monte Carlo iteration probabilities, i.e., the

likelihood that a given Monte Carlo iteration will occur relative to all

other possible iterations. Traditional Monte Carlo simulation does not

compute iteration probabilities, so designers assume that each iteration

has an equal weighting. An iteration at 3 sigma is just that -- an iteration

at 3 sigma. However, an iteration that is more likely than 50% of possible

iterations is clearly much more important than one that is more likely than

just 0.01% of possible iterations.

BDA developed a patent-pending ability to quantify every Monte Carlo

iteration's probability. The ACE Distribution Analyzer displays color-coded

stacked histogram "heat maps" of these probabilities. Iteration probability

adds a powerful new dimension to characterization which BDA will leverage

going forward.

FAST RUNTIME

ACE supports BDA Analog FastSPICE (AFS) and any HSPICE-compatible or Spectre-

compatible simulator. It currently supports AFS and HSPICE, and it will

support Spectre in 13Q3.

ACE takes advantage of AFS circuit simulator single-core performance which

is 5x-10x faster than any other foundry certified simulator. Generally the

fastest, most efficient way to run characterization on a multicore machine

is to parallelize the variants as evenly as possible across all cores. In

this mode ("multi-core parallel" or "MCP"), AFS uses 1 license for the first

core, 1 for the next 3 cores, and 1 for every 4 cores thereafter.

The runtime speedup is almost linear with the number of cores in this mode

(up to at least 32 cores), which means these runs are not only 5x-10x faster

than any other foundry certified simulator, but they 3x-4x more license

efficient, too. A standard multicore machine with a few AFS licenses has

the throughput of a small simulation farm for characterization applications.

You can also run AFS from ADE-XL and get the same performance speed-ups.

However, ADE-XL can take advantage of the AFS MCP 3x-4x license efficiency

for Monte Carlo runs only.

It is also important to perform at least limited characterization on larger

circuits. Designers use AFS to run selected corners, sweeps and even Monte

Carlo on some 1 million-plus-element circuits, e.g., top-level high-speed

I/O transceivers, post-layout ADCs, and CMOS image sensors. For those apps

ACE supports an AFS mixed-multithreading/MCP mode with the same 3x-4x

license efficiency.

OPEN CHARACTERIZATION DATA

Unlike command-line approaches where characterization data is unstructured

or ADE-XL where data is difficult to access, ACE stores all characterization

data in an Open Verification Database (OVD), where "Open" is actually open.

There are no proprietary ownership claims, license requirements, or access

restrictions. It's the design team's data. OVD makes it fully accessible.

OVD is a simple standard directory structure and a set of files for each

characterization test-variant combination. All files are in existing

industry standard formats where possible. Where there are no standards,

files intended for tools are in XML and those intended for humans are in

text. Customers and third-parties can write out in OVD format, read any OVD

data, analyze that data, change the data, add to data, etc. BDA expects

OVD to evolve to be an open standard over time.

AFS generates OVD directly today. Other simulators don't. If a designer

chooses to run a third-party simulator, ACE organizes and supplements the

third-party simulator output to be OVD compatible. BDA will do this for

leading HSPICE and Spectre-compatible simulators.

ENVIRONMENT

ACE runs standalone. ACE runs integrated with ADE (5.1). ACE runs

integrated with ADE-L (6.1). It has exactly the same look, feel, and

functionality regardless of how it is invoked. For customers that have a

mix of 2 or 3 of the above environments - even on the same project - ACE

provides a common characterization environment across the entire project.

ACE also runs in batch mode. Designers that like scripts can have at it.

Only with ACE, they'll find that a short run script replaces many 10's or

100's of lines of scripting. It also means that it is straightforward for

anyone to create regressions. Analog regressions, imagine that.

From a flow standpoint, ACE OVD enables direct third-party integration and

extension. CAD engineers, designers, and third parties (including other

analog characterization tools) can directly read and write OVD information

without any restrictions.

This makes it practical to tie analog characterization into the rest of

the IC design flow, including custom implementation, digital verification,

design management, etc.

- Paul "Pi" Estrada

Berkeley DA, Inc. Santa Clara, CA

BDA developed a patent-pending ability to quantify every Monte Carlo

iteration's probability. The ACE Distribution Analyzer displays color-coded

stacked histogram "heat maps" of these probabilities. Iteration probability

adds a powerful new dimension to characterization which BDA will leverage

going forward.

FAST RUNTIME

ACE supports BDA Analog FastSPICE (AFS) and any HSPICE-compatible or Spectre-

compatible simulator. It currently supports AFS and HSPICE, and it will

support Spectre in 13Q3.

ACE takes advantage of AFS circuit simulator single-core performance which

is 5x-10x faster than any other foundry certified simulator. Generally the

fastest, most efficient way to run characterization on a multicore machine

is to parallelize the variants as evenly as possible across all cores. In

this mode ("multi-core parallel" or "MCP"), AFS uses 1 license for the first

core, 1 for the next 3 cores, and 1 for every 4 cores thereafter.

The runtime speedup is almost linear with the number of cores in this mode

(up to at least 32 cores), which means these runs are not only 5x-10x faster

than any other foundry certified simulator, but they 3x-4x more license

efficient, too. A standard multicore machine with a few AFS licenses has

the throughput of a small simulation farm for characterization applications.

You can also run AFS from ADE-XL and get the same performance speed-ups.

However, ADE-XL can take advantage of the AFS MCP 3x-4x license efficiency

for Monte Carlo runs only.

It is also important to perform at least limited characterization on larger

circuits. Designers use AFS to run selected corners, sweeps and even Monte

Carlo on some 1 million-plus-element circuits, e.g., top-level high-speed

I/O transceivers, post-layout ADCs, and CMOS image sensors. For those apps

ACE supports an AFS mixed-multithreading/MCP mode with the same 3x-4x

license efficiency.

OPEN CHARACTERIZATION DATA

Unlike command-line approaches where characterization data is unstructured

or ADE-XL where data is difficult to access, ACE stores all characterization

data in an Open Verification Database (OVD), where "Open" is actually open.

There are no proprietary ownership claims, license requirements, or access

restrictions. It's the design team's data. OVD makes it fully accessible.

OVD is a simple standard directory structure and a set of files for each

characterization test-variant combination. All files are in existing

industry standard formats where possible. Where there are no standards,

files intended for tools are in XML and those intended for humans are in

text. Customers and third-parties can write out in OVD format, read any OVD

data, analyze that data, change the data, add to data, etc. BDA expects

OVD to evolve to be an open standard over time.

AFS generates OVD directly today. Other simulators don't. If a designer

chooses to run a third-party simulator, ACE organizes and supplements the

third-party simulator output to be OVD compatible. BDA will do this for

leading HSPICE and Spectre-compatible simulators.

ENVIRONMENT

ACE runs standalone. ACE runs integrated with ADE (5.1). ACE runs

integrated with ADE-L (6.1). It has exactly the same look, feel, and

functionality regardless of how it is invoked. For customers that have a

mix of 2 or 3 of the above environments - even on the same project - ACE

provides a common characterization environment across the entire project.

ACE also runs in batch mode. Designers that like scripts can have at it.

Only with ACE, they'll find that a short run script replaces many 10's or

100's of lines of scripting. It also means that it is straightforward for

anyone to create regressions. Analog regressions, imagine that.

From a flow standpoint, ACE OVD enables direct third-party integration and

extension. CAD engineers, designers, and third parties (including other

analog characterization tools) can directly read and write OVD information

without any restrictions.

This makes it practical to tie analog characterization into the rest of

the IC design flow, including custom implementation, digital verification,

design management, etc.

- Paul "Pi" Estrada

Berkeley DA, Inc. Santa Clara, CA

Join

Index

Next->Item

|

|