( ESNUG 523 Item 6 ) -------------------------------------------- [05/02/13]

Subject: SPICE user-share numbers and Solido's militant SPICE neutrality

> - SCOOP! In today's ESNUG 521 #5 you'll see that Solido has quietly

> added "netlist-only" Spectre input support. Helps Cadence break

> the memory/std cell SPICE monopoly Aart bought with Magma. YAY!

>

> - from http://www.deepchip.com/items/0521-03.html

From: [ Amit Gupta of Solido Design ]

Hi John,

Your rumor is half right and half wrong. Solido did just release a version

of Variation Designer that supports Cadence Spectre with netlist-only input.

We see a growing trend of Solido's customers using Spectre for memory and

standard cell design. However, interpreting this to mean that Solido is

teaming up with Cadence against Synopsys would be absolutely wrong.

WE DON'T TAKE SIDES

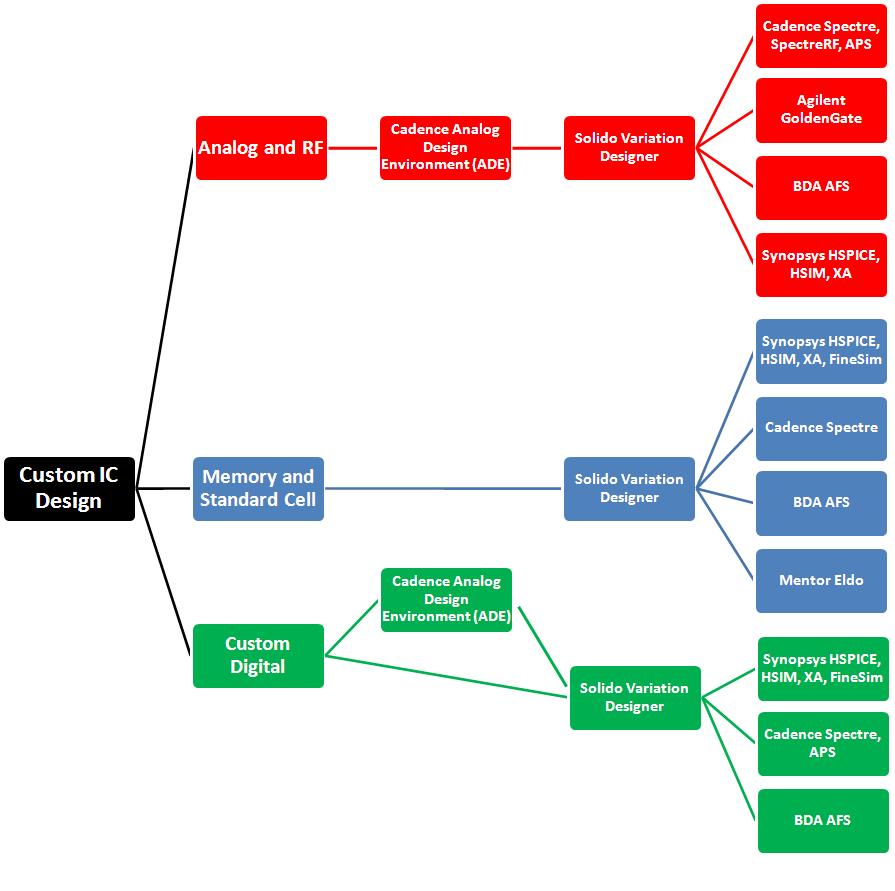

Solido is simulator vendor neutral, is partnered with and fully supports ALL

the 10 major SPICE simulators including Cadence Spectre/SpectreRF/APS,

Synopsys HSPICE/HSIM/XA/FineSim (3X faster integration announced in April),

BDA AFS, Mentor Eldo, and Agilent GoldenGate. Solido Variation Designer is

also integrated with Cadence Analog Design Environment (through the Cadence

Connections program).

Solido intentionally decided not to build its own simulator -- we let our

users pick their preferred SPICE vendor. Solido focuses on figuring out

*what* to simulate, giving better design coverage in fewer simulations than

brute force PVT corner and 3- to 6-sigma Monte Carlo analysis. No wasted

simulations! Plus it lets designers run their simulation jobs across 10's or

100's of simulator nodes in parallel.

To demonstrate our simulation reduction capability and improved design

coverage on various simulators, below are some recent customer benchmarks:

PVT Corner 3-sigma 6-sigma

Analysis Monte Carlo Monte Carlo

----------- ---------- -----------

Design size 1500 devices 20 devices 50 devices

Simulator Cadence Spectre BDA AFS Synopsys HSPICE

Brute force # sims 6,561 5,000 5 billion *

Total sim time 55 hrs 21 hrs N/A*

Solido # sims 83 455 4,300

Total sim time 42 mins 2 hrs 2.5 hrs

Solido simulation

reduction 79x 11x 1,162,791X

* - Of course, no one actually runs 5 billion Monte Carlo simulations

as that would take years, but Solido's 6-sigma solution gives the

design coverage accuracy of 5 B simulations in 4,300 simulations.

Below is a current snapshot of the custom IC design world of our users:

Here is an approximate breakdown of simulator seats run by Solido Variation

Designer by application area:

Memory and Standard Cell: ########################## 53%

Analog and RF: ################ 32%

Custom Digital: ######## 15%

Here is a current snapshot of the approximate breakdown of simulator seats

our customers are running with Solido Variation Designer, by simulation

vendor. (NOTE - these numbers are dynamic and can change at any time):

Synopsys HSPICE/HSIM/XA/FineSim: ######################## 61%

Cadence Spectre/SpectreRF/APS: ######### 23%

BDA AFS: ##### 13%

Agilent GoldenGate: # 2%

Mentor Eldo: 1%

The Cadence numbers look lower than expected, but this is because users

consume far more simulator seats for memory (since design for 6-sigma yield

is a must) and standard cell design (because libraries include many designs)

than the other custom IC application areas. This is why the major

simulation vendors are targeting these sectors so aggressively.

- Amit Gupta

Solido Design Vancouver, Canada

Here is an approximate breakdown of simulator seats run by Solido Variation

Designer by application area:

Memory and Standard Cell: ########################## 53%

Analog and RF: ################ 32%

Custom Digital: ######## 15%

Here is a current snapshot of the approximate breakdown of simulator seats

our customers are running with Solido Variation Designer, by simulation

vendor. (NOTE - these numbers are dynamic and can change at any time):

Synopsys HSPICE/HSIM/XA/FineSim: ######################## 61%

Cadence Spectre/SpectreRF/APS: ######### 23%

BDA AFS: ##### 13%

Agilent GoldenGate: # 2%

Mentor Eldo: 1%

The Cadence numbers look lower than expected, but this is because users

consume far more simulator seats for memory (since design for 6-sigma yield

is a must) and standard cell design (because libraries include many designs)

than the other custom IC application areas. This is why the major

simulation vendors are targeting these sectors so aggressively.

- Amit Gupta

Solido Design Vancouver, Canada

Join

Index

Next->Item

|

|