( ESNUG 523 Item 5 ) -------------------------------------------- [05/02/13]

From: [ Shawn McCloud of Calypto ]

Subject: 648 engineers surveyed on RTL Power Reduction and HLS techniques

Hi, John,

Calypto just completed its annual blind worldwide survey. A total of 648

engineers and engineering managers responded. Our survey has two parts:

- RTL Power Reduction. This is Calypto's 2nd annual survey. Our

2012 RTL power reduction survey you published in ESNUG 498 #4.

- High Level Synthesis. It's our 5th year surveying on HLS.

Prior surveys are ESNUG 479 #4, 486 #7, 488 #4, and 513 #4.

Here's out latest 2013 survey results:

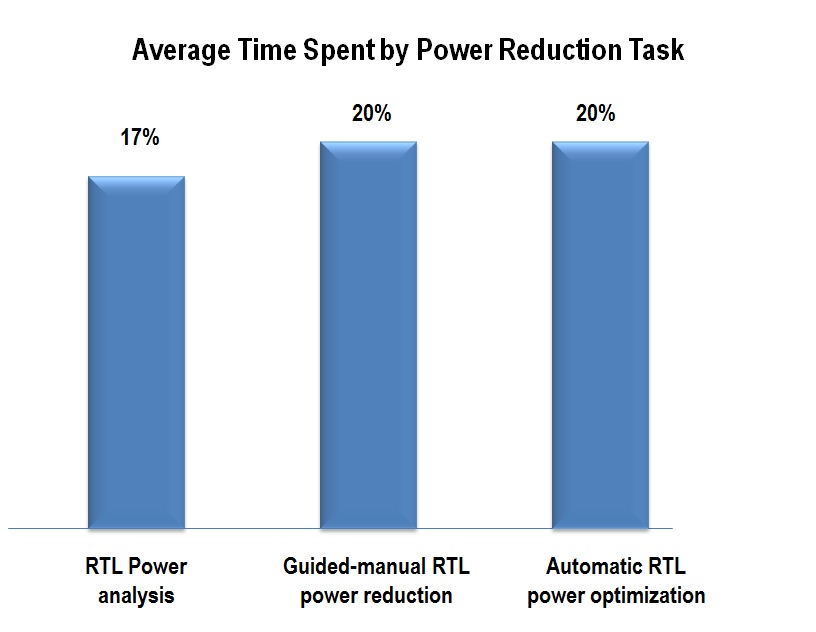

AVERAGE TIME SPENT ON POWER REDUCTION TASKS

Question 1: "What percentage of your time do you spend on each

of these RTL power stages?"

These results emphasize how the methods used to reduce RTL power are really

balanced between 3 different areas: analysis, guided/manual, and automatic

power reduction. The reality is RTL power optimization must incorporate a

mix of techniques to reduce power across the entire SoC.

For new blocks, designers use analysis and guided optimization to help

identify wasted power as well as make recommendations for ways to improve

power consumption. Later, they can use automated optimization for an

additional power savings at the end of the design process.

For IP reuse or RTL reuse, where there's limited knowledge of the block's

internals because the engineer who created the block is gone (or not even

known), automatic optimization with deep sequential analysis is the only

way to get high return clock-gating and memory-gating logic. In addition,

these automatic flows also require sequential logic equivalency checking

to formally prove the automated changes didn't add any functional errors.

ORGANIZATIONAL PLANS FOR POWER REDUCTION TOOLS FOR 2013

Question 2: "What are your 2013 plans for RTL power reduction tools?"

These results emphasize how the methods used to reduce RTL power are really

balanced between 3 different areas: analysis, guided/manual, and automatic

power reduction. The reality is RTL power optimization must incorporate a

mix of techniques to reduce power across the entire SoC.

For new blocks, designers use analysis and guided optimization to help

identify wasted power as well as make recommendations for ways to improve

power consumption. Later, they can use automated optimization for an

additional power savings at the end of the design process.

For IP reuse or RTL reuse, where there's limited knowledge of the block's

internals because the engineer who created the block is gone (or not even

known), automatic optimization with deep sequential analysis is the only

way to get high return clock-gating and memory-gating logic. In addition,

these automatic flows also require sequential logic equivalency checking

to formally prove the automated changes didn't add any functional errors.

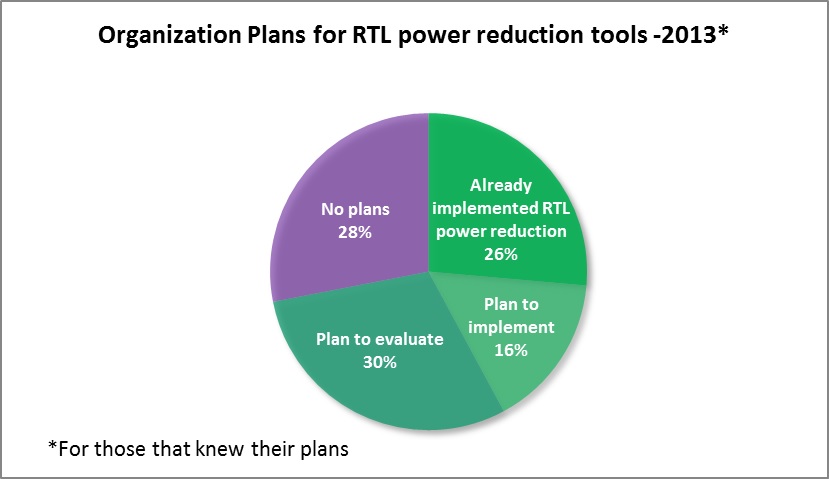

ORGANIZATIONAL PLANS FOR POWER REDUCTION TOOLS FOR 2013

Question 2: "What are your 2013 plans for RTL power reduction tools?"

For the 561 respondents that knew their organization’s RTL power reduction

tool adoption plans, 42 percent have already implemented RTL power reduction

tools or plan to do so in 2013 (26% plus 16%).

The combined total organizational involvement with RTL power reduction is

72 percent. This shows a high degree of industry activity in this sector

for 2013. The big power consumption changes must be made at the RTL level;

or in the architecture level -- gate level power reduction is too late.

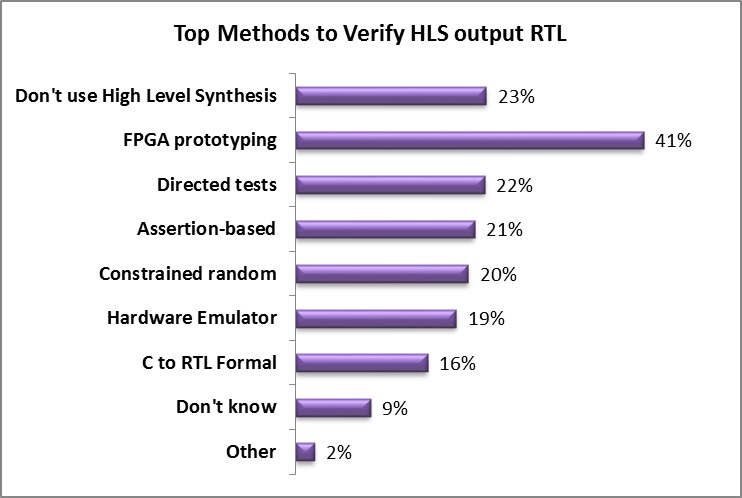

TOP METHODS OF VERIFYING HLS-GENERATED RTL OUTPUT

Question 3: "Please select your organization's top *2* methods to

verify your RTL output from High Level Synthesis."

For the 561 respondents that knew their organization’s RTL power reduction

tool adoption plans, 42 percent have already implemented RTL power reduction

tools or plan to do so in 2013 (26% plus 16%).

The combined total organizational involvement with RTL power reduction is

72 percent. This shows a high degree of industry activity in this sector

for 2013. The big power consumption changes must be made at the RTL level;

or in the architecture level -- gate level power reduction is too late.

TOP METHODS OF VERIFYING HLS-GENERATED RTL OUTPUT

Question 3: "Please select your organization's top *2* methods to

verify your RTL output from High Level Synthesis."

The top method for verifying RTL from High Level Synthesis was FPGA

prototyping. There was a range of usage among the other verification

methods: Directed tests, Assertion-based, Constrained random, Hardware

emulation, and C-to-RTL formal.

INTERESTING CONTRAST: In last year's HLS survey, C-to-RTL formal ranked as

the #3 most important technology to integrate with HLS, following RTL

synthesis and Power Analysis/Optimization. (See ESNUG 513 #4.) Yet this

year's survey shows that of all the verification techniques employed,

C-to-RTL formal is the least used. I believe the major gap between what

designers want and what is actually deployed is because C-to-RTL formal

tools haven't sufficiently integrated into HLS to be generally deployable

for current designs.

This need for deep integration of C-to-RTL formal (SLEC) and SystemC/C++

HLS (Catapult) was a driving reason for the merger of Catapult from Mentor

into Calypto. Another outcome of the merger was we then embedded Calypto

PowerPro under-the-hood of Catapult to create Catapult LP which lets

hardware engineers optimize power at the architectural level -- where the

biggest impact on power can be made.

This year's survey showed RTL power reduction techniques are balanced across

guided/manual and automatic optimization. To that end, PowerPro utilizes

deep sequential analysis -- originally developed in SLEC -- to look across

100's of registers to find the maximum power savings possible for *both*

guided/manual and automated modes.

- Shawn McCloud

Calypto Design San Jose, CA

The top method for verifying RTL from High Level Synthesis was FPGA

prototyping. There was a range of usage among the other verification

methods: Directed tests, Assertion-based, Constrained random, Hardware

emulation, and C-to-RTL formal.

INTERESTING CONTRAST: In last year's HLS survey, C-to-RTL formal ranked as

the #3 most important technology to integrate with HLS, following RTL

synthesis and Power Analysis/Optimization. (See ESNUG 513 #4.) Yet this

year's survey shows that of all the verification techniques employed,

C-to-RTL formal is the least used. I believe the major gap between what

designers want and what is actually deployed is because C-to-RTL formal

tools haven't sufficiently integrated into HLS to be generally deployable

for current designs.

This need for deep integration of C-to-RTL formal (SLEC) and SystemC/C++

HLS (Catapult) was a driving reason for the merger of Catapult from Mentor

into Calypto. Another outcome of the merger was we then embedded Calypto

PowerPro under-the-hood of Catapult to create Catapult LP which lets

hardware engineers optimize power at the architectural level -- where the

biggest impact on power can be made.

This year's survey showed RTL power reduction techniques are balanced across

guided/manual and automatic optimization. To that end, PowerPro utilizes

deep sequential analysis -- originally developed in SLEC -- to look across

100's of registers to find the maximum power savings possible for *both*

guided/manual and automated modes.

- Shawn McCloud

Calypto Design San Jose, CA

Join

Index

Next->Item

|

|