( ESNUG 521 Item 6 ) -------------------------------------------- [03/28/13]

From: [ Denis Dutoit of CEA-Leti ]

Subject: Spyglass Power for both architectural and RTL power reduction

Hi, John,

We've used Atrenta Spyglass Power for about 2 years. Our typical projects

tend to run 10-12 months. I would estimate we've had a 2 months savings

with it. That's roughly a 17% project time savings for us.

At my company we have 2 primary types of Spyglass users:

1) Architects,

and 2) Senior Power Designers.

Our architects use Spyglass at the architectural level as follows:

1. Our architect uses our internal RTL generator to generate

RTL code with a reconfigurable clusterized architecture;

without doing any clock gating yet.

2. The architect then runs Spyglass Power to find power bugs.

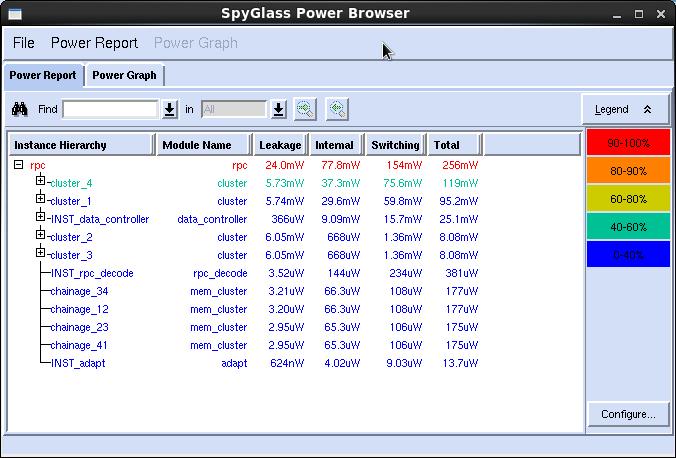

Power figures for hierarchical modules

There is a feature of Spyglass Power which gives you a graph of

every activity in the design, allowing us to see the activity is

for a particular block, even without actually doing any power

computations.

3. In one case, the architect found a power bug which affected 96% of

our programmable core.

Power figures for hierarchical modules

There is a feature of Spyglass Power which gives you a graph of

every activity in the design, allowing us to see the activity is

for a particular block, even without actually doing any power

computations.

3. In one case, the architect found a power bug which affected 96% of

our programmable core.

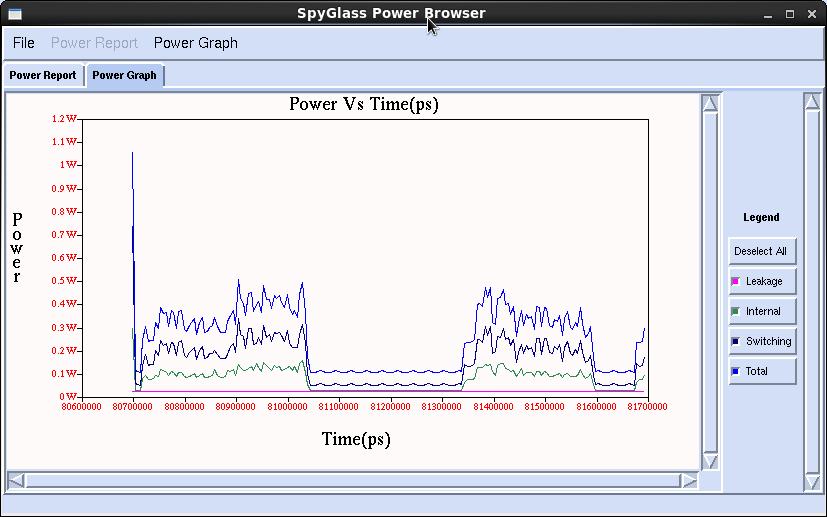

Power graph for architecture

This was a situation where the Spyglass Power activity report showed

that a cluster of the design that should have been in an idle state

was active and drawing power when it shouldn't have been.

4. The architect removed these power bugs by manually adding clock-

gating cells at the cluster-level.

5. He then did final analysis for clock-gating. We can extract a lot

of different reports with Spyglass, such as what is clocked and

what is not clocked; this helps to guide us in developing

micro-architecture.

6. We then used Spyglass' power optimization which gave us a power

savings from 9% to 45% at the architectural level when running a

set of benchmarks.

---- ---- ---- ---- ---- ---- ----

MICRO-ARCHITECTURE POWER ESTIMATES:

We came up with a clever way to use Spyglass to create a power model to

analyze power consumption and optimize our programmable core design at the

architectural level.

a. We had a complete instruction set for our small RISC CPU. For

every instruction and couple of instructions, we generated

different simulation vectors.

b. We input simulation vectors to Spyglass, to get power estimates.

c. We wrote a C program to compile these individual power estimates,

taking in account their duration, to create a power scorecard

for the CPU.

From here we could estimate/analyze our microarchitecture power budget.

The register file was our greediest module. This opportunity to consider

programmable architectures in terms of power consumption especially makes

sense for compiler and hardware designers looking for power saving.

---- ---- ---- ---- ---- ---- ----

RTL POWER REDUCTION CASE STUDIES:

The other primary users of Spyglass power are our experts in low-power

design. These are highly skilled designers who usually assume that a tool

cannot do better than they can!

We have recently used Spyglass on two different chips; below I have 4 sample

case studies of our power reduction results.

Design Size Power before Power after Power

Type (registers) Spyglass Spyglass Reduction

1 Ultra-low 11,821 12.1 mW 11.8 mW 2%

power

DSP core

2 Bit level 5,504 67.4 mW 58.7 mW 13%

translation

inside

3GPP-LTE

3 BCJR turbo 3,286 108.0 mW 88.3 mW 18%

decoder (+ 10 memories)

inside

3GPP-LTE

For each of the above case studies, the power reduction was done using

either Spyglass' manual/guided optimization or automated optimization modes

as follows:

1. automated

2. guided

3. automated

Design 1: The initial power reduction done by one of our best local

designers. Even so Spyglass got us another 2% reduction.

Spyglass Power looked at every single register and memory

inside the block -- there can be 10,000's of them -- to see

if it could gate them. It then optimized the remaining

registers/flip-flops, which were impossible for us to find

by hand.

Design 2: Most of the 13% power reduction came from Spyglass

automatically gating registers/flip-flops.

Design 3: Most of the 18% power reduction came from Spyglass' memory

gating. The memory power reduction comes from rules such as:

chip select gating, redundant read, and redundant write.

Spyglass' automated optimization often finds more opportunities for power

reduction optimization beyond our manual/guided manual optimization.

Typically, this second stage includes optimizations focused on applying

specific sequential and formal techniques to reduce register and memory

power.

---- ---- ---- ---- ---- ---- ----

POWER ESTIMATION:

We've run a lot of correlations to assess for Spyglass' power estimation

accuracy. It is within 2% to 10% of our golden power sign-off, which is

Synopsys Primetime Power. Suffice to say, that is absolutely precise enough

to make design decisions for power reduction.

If we do not have simulation vectors, then Spyglass can work with default

activity parameters to provide rough estimation. This was useful for power

planning at SoC level during early design development phase (SoC power

architecture specification). However, for detailed power optimization

during the RTL design phase, we need simulation vectors to get sufficient

accuracy.

---- ---- ---- ---- ---- ---- ----

USING SPYGLASS POWER IN OUR DESIGN FLOW:

First we run simulation vectors to functionally verify our design; we mostly

design in VHDL, with some Verilog.

Next, we run Spyglass Power, using the simulation vectors. Spyglass has no

problems with mixed language support. We can instantiated a VHDL module

within Verilog, and we can instantiated a Verilog module within Verilog.

Vector Vector Spyglass Power

Example Format File Size Load time

------- ------ --------- ---------

1 vcd 1.5 GB 4 min

2 vcd 20.0 MB 5 sec

Spyglass Power input:

- RTL code. Spyglass supports: Verilog, VHDL, System Verilog

- Library files

- Simulation vectors. Spyglass supports: .fsdb, .vcd and .saif.

Spyglass Power output:

- Written reports on activity and power consumption, such as

enable scorecards, clock-gating efficiency report, power

profiling report (blocks, clock domains, registers).

- If we use the automated optimization, it gives us modified RTL

When we do power transformations, there is a chance that you change design

behavior. Spyglass' sequential analysis and equivalence checking lets us

test this. Spyglass will automatically compare the modified RTL to the

original RTL, along with pass/fail reports, using a formal engine built

right into the tool. We use it, it works.

---- ---- ---- ---- ---- ---- ----

CONCLUSION:

Spyglass' design flow integration allows our designers to focus on the

results of the tool: power estimation and optimization.

We are a silicon conductor research institute. We work on advanced design

technologies with industrial partners such as ST Microelectronics. Our two

main applications today are advanced telecom basebands and multi-processor

SoC's for computing.

We have used Spyglass on recent designs with up to 1 Ghz clock speeds, and

are implemented in ST Micro 28 nm process, with Silicon on Insulator (SOI).

It's part of our mainstream design flow, and all the evidence is that

Spyglass Power will meet the needs of our new designs, which will be up to

2.5 Ghz and use a 14 nm process.

We are looking at new design optimization techniques using the substrate,

based on substrate polarization that changes, for example, the transistor

power consumption and speed. We intend, in the coming weeks, to use

Spyglass Power for defining (using its power estimation feature) the right

set of operating points (voltage, frequency) for our Dynamic Voltage and

Frequency Scaling.

We are happy with Spyglass. So far, we haven't seen any serious problems.

The tool is stable and we get same-day support. We have Atrenta R&D close

by, we know the Atrenta R&D folks, and cooperate well.

I would like to also thank Ahmed Jerraya and Erwan Piriou, who cooperated

with me on this eval.

- Denis Dutoit

CEA-Leti Institute Grenoble, France

Power graph for architecture

This was a situation where the Spyglass Power activity report showed

that a cluster of the design that should have been in an idle state

was active and drawing power when it shouldn't have been.

4. The architect removed these power bugs by manually adding clock-

gating cells at the cluster-level.

5. He then did final analysis for clock-gating. We can extract a lot

of different reports with Spyglass, such as what is clocked and

what is not clocked; this helps to guide us in developing

micro-architecture.

6. We then used Spyglass' power optimization which gave us a power

savings from 9% to 45% at the architectural level when running a

set of benchmarks.

---- ---- ---- ---- ---- ---- ----

MICRO-ARCHITECTURE POWER ESTIMATES:

We came up with a clever way to use Spyglass to create a power model to

analyze power consumption and optimize our programmable core design at the

architectural level.

a. We had a complete instruction set for our small RISC CPU. For

every instruction and couple of instructions, we generated

different simulation vectors.

b. We input simulation vectors to Spyglass, to get power estimates.

c. We wrote a C program to compile these individual power estimates,

taking in account their duration, to create a power scorecard

for the CPU.

From here we could estimate/analyze our microarchitecture power budget.

The register file was our greediest module. This opportunity to consider

programmable architectures in terms of power consumption especially makes

sense for compiler and hardware designers looking for power saving.

---- ---- ---- ---- ---- ---- ----

RTL POWER REDUCTION CASE STUDIES:

The other primary users of Spyglass power are our experts in low-power

design. These are highly skilled designers who usually assume that a tool

cannot do better than they can!

We have recently used Spyglass on two different chips; below I have 4 sample

case studies of our power reduction results.

Design Size Power before Power after Power

Type (registers) Spyglass Spyglass Reduction

1 Ultra-low 11,821 12.1 mW 11.8 mW 2%

power

DSP core

2 Bit level 5,504 67.4 mW 58.7 mW 13%

translation

inside

3GPP-LTE

3 BCJR turbo 3,286 108.0 mW 88.3 mW 18%

decoder (+ 10 memories)

inside

3GPP-LTE

For each of the above case studies, the power reduction was done using

either Spyglass' manual/guided optimization or automated optimization modes

as follows:

1. automated

2. guided

3. automated

Design 1: The initial power reduction done by one of our best local

designers. Even so Spyglass got us another 2% reduction.

Spyglass Power looked at every single register and memory

inside the block -- there can be 10,000's of them -- to see

if it could gate them. It then optimized the remaining

registers/flip-flops, which were impossible for us to find

by hand.

Design 2: Most of the 13% power reduction came from Spyglass

automatically gating registers/flip-flops.

Design 3: Most of the 18% power reduction came from Spyglass' memory

gating. The memory power reduction comes from rules such as:

chip select gating, redundant read, and redundant write.

Spyglass' automated optimization often finds more opportunities for power

reduction optimization beyond our manual/guided manual optimization.

Typically, this second stage includes optimizations focused on applying

specific sequential and formal techniques to reduce register and memory

power.

---- ---- ---- ---- ---- ---- ----

POWER ESTIMATION:

We've run a lot of correlations to assess for Spyglass' power estimation

accuracy. It is within 2% to 10% of our golden power sign-off, which is

Synopsys Primetime Power. Suffice to say, that is absolutely precise enough

to make design decisions for power reduction.

If we do not have simulation vectors, then Spyglass can work with default

activity parameters to provide rough estimation. This was useful for power

planning at SoC level during early design development phase (SoC power

architecture specification). However, for detailed power optimization

during the RTL design phase, we need simulation vectors to get sufficient

accuracy.

---- ---- ---- ---- ---- ---- ----

USING SPYGLASS POWER IN OUR DESIGN FLOW:

First we run simulation vectors to functionally verify our design; we mostly

design in VHDL, with some Verilog.

Next, we run Spyglass Power, using the simulation vectors. Spyglass has no

problems with mixed language support. We can instantiated a VHDL module

within Verilog, and we can instantiated a Verilog module within Verilog.

Vector Vector Spyglass Power

Example Format File Size Load time

------- ------ --------- ---------

1 vcd 1.5 GB 4 min

2 vcd 20.0 MB 5 sec

Spyglass Power input:

- RTL code. Spyglass supports: Verilog, VHDL, System Verilog

- Library files

- Simulation vectors. Spyglass supports: .fsdb, .vcd and .saif.

Spyglass Power output:

- Written reports on activity and power consumption, such as

enable scorecards, clock-gating efficiency report, power

profiling report (blocks, clock domains, registers).

- If we use the automated optimization, it gives us modified RTL

When we do power transformations, there is a chance that you change design

behavior. Spyglass' sequential analysis and equivalence checking lets us

test this. Spyglass will automatically compare the modified RTL to the

original RTL, along with pass/fail reports, using a formal engine built

right into the tool. We use it, it works.

---- ---- ---- ---- ---- ---- ----

CONCLUSION:

Spyglass' design flow integration allows our designers to focus on the

results of the tool: power estimation and optimization.

We are a silicon conductor research institute. We work on advanced design

technologies with industrial partners such as ST Microelectronics. Our two

main applications today are advanced telecom basebands and multi-processor

SoC's for computing.

We have used Spyglass on recent designs with up to 1 Ghz clock speeds, and

are implemented in ST Micro 28 nm process, with Silicon on Insulator (SOI).

It's part of our mainstream design flow, and all the evidence is that

Spyglass Power will meet the needs of our new designs, which will be up to

2.5 Ghz and use a 14 nm process.

We are looking at new design optimization techniques using the substrate,

based on substrate polarization that changes, for example, the transistor

power consumption and speed. We intend, in the coming weeks, to use

Spyglass Power for defining (using its power estimation feature) the right

set of operating points (voltage, frequency) for our Dynamic Voltage and

Frequency Scaling.

We are happy with Spyglass. So far, we haven't seen any serious problems.

The tool is stable and we get same-day support. We have Atrenta R&D close

by, we know the Atrenta R&D folks, and cooperate well.

I would like to also thank Ahmed Jerraya and Erwan Piriou, who cooperated

with me on this eval.

- Denis Dutoit

CEA-Leti Institute Grenoble, France

Join

Index

Next->Item

|

|