( ESNUG 488 Item 2 ) -------------------------------------------- [03/01/11]

From: [ Remember The Alamo ]

Subject: Hogan keynote on SOC, IP, Design Management, Verification, EDA360

Hi John,

Please keep me anonymous.

I attended Jim Hogan's keynote yesterday. The NASCUG'11 SystemC event was

co-located with DVCon'11. Jim covered a lot of ground. He reminded me of

Wally Rhines. Lots of hard data and some humor to wake everyone up.

1. The semiconductor industry is going toward SOCs

Semiconductors are no longer just an IC business - this is

being driven in part by the fact that:

SoC margins: ############################## 40-60%

Discrete IC margins: ########## 10-20%.

SOC's are non-processor centric, e.g. multi-CPU, HW accelerators, etc

and involve heterogeneous configurable compute fabrics, i.e. FPGAs.

2. IP is integral part of SOC

Jim showed IC Insights' top 20 semiconductor sales leaders and pointed

out that 11 of them now license ARM.

He also had data from Wharton-GSA which showed more internal IP and

more new IP than expected.

propriety IP: ################################# 66%

foundry IP: ######### 18%

3rd party IP: ######## 16%

plus

new IP: ###################### 44%

derivative IP: ################################ 63%

3. Designer impact: Design Management, Assembly, and Verification

These trends above bring two main concerns for SOC design teams:

- Assembly and management. Internal and external IP is driven

from IP vendor directories, and engineers/management need to:

1. control access to IP data

2. ensure IP data is compatible with their internal

design environment

3. track IP usage (especially if paying royalties on it)

4. manage constraints for hard and soft IP

- Verification to validate IP quality and functionality.

E.g. Does your IP work? Does it work with your design

specification? Does it work in your derivative designs?

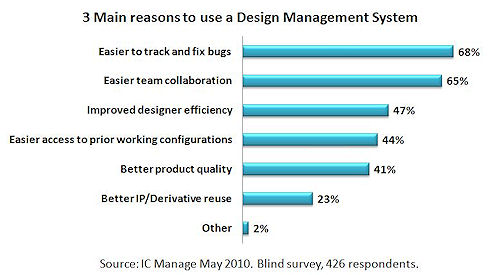

- Derivative designs further complicate both IP & bug traceability,

making it harder to find original instances. Plus you need to

propagate changes through all revisions and derivatives. Hogan

showed a design derivative tree of how one early bug impacted

12 releases. Said bug tracking is driving reason for design data

management.

He also had data from Wharton-GSA which showed more internal IP and

more new IP than expected.

propriety IP: ################################# 66%

foundry IP: ######### 18%

3rd party IP: ######## 16%

plus

new IP: ###################### 44%

derivative IP: ################################ 63%

3. Designer impact: Design Management, Assembly, and Verification

These trends above bring two main concerns for SOC design teams:

- Assembly and management. Internal and external IP is driven

from IP vendor directories, and engineers/management need to:

1. control access to IP data

2. ensure IP data is compatible with their internal

design environment

3. track IP usage (especially if paying royalties on it)

4. manage constraints for hard and soft IP

- Verification to validate IP quality and functionality.

E.g. Does your IP work? Does it work with your design

specification? Does it work in your derivative designs?

- Derivative designs further complicate both IP & bug traceability,

making it harder to find original instances. Plus you need to

propagate changes through all revisions and derivatives. Hogan

showed a design derivative tree of how one early bug impacted

12 releases. Said bug tracking is driving reason for design data

management.

- Jim had data from IC Manage showing 47% of management cited delays

due to design management issues, and 30% of organizations had a

commercial design data management system in 2010. He had problems

with DM way back in his National Semiconductor days, said it's a

"must-care" issue for design managers.

4. SOC Realization

Jim said Cadence had established a good lexicon for the industry with

their EDA360 mission. He liked Cadence's EDA360 terminology for

- System Realization

- SOC Realization (architectural individual SOC)

- Silicon Realization (classic EDA, with a lot of ASIC)

Jim said SOC Realization needed IP selection and management, design

assembly, feasibility checks (PPA) and bare-metal software development.

It required design data management (for assembly and verification),

debug and analysis tools, software models and memory and controllers.

He closed his talk with a chart on SOC realization which had a detailed list

of ~70 technologies that he said was his shopping list for companies, under

the major categories of IP Sourcing, SoC Creation, and SoC Handoff. He said

this is where there is money to be made over the next 5 years.

- [ Remember The Alamo ]

- Jim had data from IC Manage showing 47% of management cited delays

due to design management issues, and 30% of organizations had a

commercial design data management system in 2010. He had problems

with DM way back in his National Semiconductor days, said it's a

"must-care" issue for design managers.

4. SOC Realization

Jim said Cadence had established a good lexicon for the industry with

their EDA360 mission. He liked Cadence's EDA360 terminology for

- System Realization

- SOC Realization (architectural individual SOC)

- Silicon Realization (classic EDA, with a lot of ASIC)

Jim said SOC Realization needed IP selection and management, design

assembly, feasibility checks (PPA) and bare-metal software development.

It required design data management (for assembly and verification),

debug and analysis tools, software models and memory and controllers.

He closed his talk with a chart on SOC realization which had a detailed list

of ~70 technologies that he said was his shopping list for companies, under

the major categories of IP Sourcing, SoC Creation, and SoC Handoff. He said

this is where there is money to be made over the next 5 years.

- [ Remember The Alamo ]

Join

Index

Next->Item

|

|