( ESNUG 487 Item 5 ) -------------------------------------------- [02/01/11]

From: Amit Gupta <gupta=user domain=solidodesign got calm>

Subject: A survey of 486 custom IC engineers on when variation bites you

Hi, John,

Solido had an outside consultancy run a blind global survey on custom IC

design. A total of 486 engineers and engineering managers responded.

Over half the companies surveyed have had delays due to variation, where we

defined design variation as the variation in parametric results caused by

process and environmental (PVT) variation, random variation,

layout-dependent (proximity) effects, and parasitics.

"Have you or your organization ever missed a project deadline, delayed

a tapeout, or had to do a respin due to variation effects?"

Yes : ###################### 53%

No : ############# 30%

Don't know : ####### 17%

For those that knew the length of delay due to variation, the average was

two work-months. I normalized the responses below to calculate the average.

"What was the average delay due to variation issues?"

1-2 days : # 2%

3-5 days : ## 4%

1-2 weeks : ##### 12%

3-4 weeks : ###### 14%

1-2 months : ######## 20%

3-6 months : ###### 14%

>6 months : ## 4%

Don't know : ############# 30%

Further, the respondents ranked variation-aware design as the #1 area

needing technology focus versus other custom IC design segments.

"In what 3 areas of Custom IC design is the most

advancement needed over the next 2 years?"

Variation-Aware Design : ############################ 66%

Parasitic Extraction : #################### 48%

Simulation : ################### 44%

Physical Verification : ################# 40%

Layout : ########### 26%

Routing : ########## 24%

Schematic Capture : ### 7%

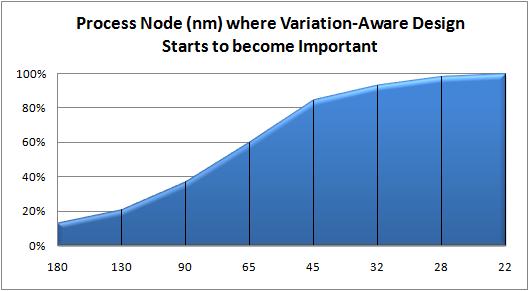

Another piece of data that your readers might find interesting is on what

process nodes the respondents saw variation as an issue. Over a third

(37%) saw it affecting designs at 90 nanometers, going up to 60% at 65

nanometers and 85% at 45 nanometers. In fact, TSMC and STARC recently

added variation-aware design to their analog/mixed-signal reference flows.

Finally, the users were very specific on which custom IC design tools they

felt needed to handle variation.

"Which of the following tools should be integrated

with variation-aware products?"

Layout editors : ############################ 66%

True SPICE simulators : ####################### 55%

Fast SPICE simulators : ###################### 52%

Schematic capture : #################### 46%

other : # 2%

With regard to the above user responses, their interest in layout-induced

variation is likely driven by layout-dependent proximity and parasitic

effects which are becoming first order effects at small nanometers. As the

survey data confirms, Solido has also been getting requests for our

variation-aware design tools to support not only true SPICE simulators but

more fast SPICE simulators as well.

- Amit Gupta

Solido DA, Inc. Saskatoon, Canada

Finally, the users were very specific on which custom IC design tools they

felt needed to handle variation.

"Which of the following tools should be integrated

with variation-aware products?"

Layout editors : ############################ 66%

True SPICE simulators : ####################### 55%

Fast SPICE simulators : ###################### 52%

Schematic capture : #################### 46%

other : # 2%

With regard to the above user responses, their interest in layout-induced

variation is likely driven by layout-dependent proximity and parasitic

effects which are becoming first order effects at small nanometers. As the

survey data confirms, Solido has also been getting requests for our

variation-aware design tools to support not only true SPICE simulators but

more fast SPICE simulators as well.

- Amit Gupta

Solido DA, Inc. Saskatoon, Canada

Join

Index

Next->Item

|

|