( ESNUG 588 Item 19 ) --------------------------------------------- [07/17/20]

Subject: Sawicki's DRC/LVS minions to launch quickie LVS linter at DAC'20

DAC'20 SCOOP - one of my spies sent me screenshots of what Joe Sawicki's

Calibre group is launching for Virtual DAC'20 next week. Sawicki's new

tool is called Calibre nmLVS-Recon, and it's essentially a linter for

circuit verification engineers to run on their raw, early-draft/dirty

designs.

If the name sounds familiar, it's the LVS counterpart to Calibre nmDRC-Recon

that Mentor announced at DAC'19 for physical verification engineers; which

they like because it saves them cycles in their DRC runs.

I asked my spy: "is Recon-LVS just like Recon-DRC's twin?" His response:

"Look John, when we run DRC or LVS the first time at the large block

level, the whole thing lights up with circuit errors that I have to

go fix. I know I am gonna see tons of shorts right off. The problem

is I have to wait for the entire OVERNIGHT RUN to finish before I can

start to fix all those shorts. Maybe I could pare down the foundry

PDK to detect shorts-only -- but that would get me fired. That's

where these quickie Recon physical linting tools help."

He went on saying later revs of Recon will supposedly lint for other types

of violations, but right now it's only about finding and fixing shorts.

Why?

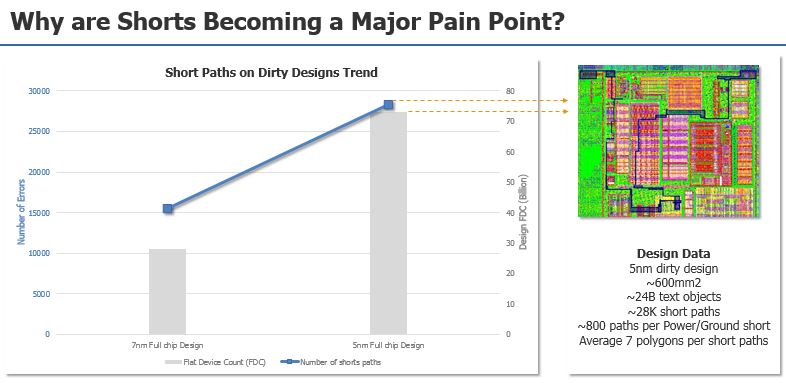

According to the Mentor slides, as transistor counts move from 30 B at 7nm

to ~70 B at 5nm, the number of short circuits are exploding. In the dirty

design below, there are 28 K shorts paths, an average of 1 short for every

7 polygons/transistors.

(click on pic to enlarge image)

|

These shorts are mainly caused by flaws in Innovus/ICC/ICC2/Fusion Compiler

PnR tools -- but can also be caused by user error -- when somebody nudges a

block in the design and everything gets misaligned, etc. You can burn

weeks trying find and fix shorts. So if you can get shorts out of the way

early, you can use that free time on other more pressing tasks.

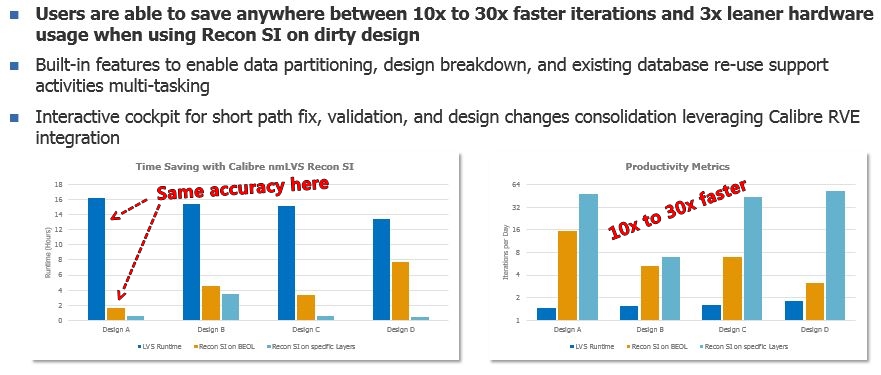

The Mentor sales pitch goes on to claim Recon DRC/LVS has the exact same

accuracy as full sign-off Calbre DRC/LVS but Recon runs 10x faster.

(click on pic to enlarge image)

|

Here's where Mentor plans to expand Recon to also do selective ERC, soft

connectivity conflict analysis, and circuit/layout comparisons without

having to tweak PDKs.

Here's what I found out when I asked for this to be explained more.

The Calibre Recon-SI flow

Setup to run Calibre, then you are ready for Calibre Recon. The inputs are

the same (GDSII or Oasis, and foundry PDK) from PnR tools (Innovus, ICC/ICC2/

Fusion, Nitro) and custom layout tools (Virtuoso, Tanner, & Custom Compiler).

You specify "-recon -si" on the command line or invocation GUI and you get a

cut-down version of LVS. The output of circuit errors is the same with no

loss in accuracy but 10X faster. Automatically, Calibre Recon SI will do just

a search for shorts in your design.

For Short Isolation, selective connectivity extraction is done to construct

the required paths for short isolation analysis. Also does data re-use and

automatic partitioning for fast TAT on the original and subsequent runs.

Lastly, the output of circuit errors looks just like any other Calibre run,

so the designer can debug with Calibre RVE interactively.

The result is faster feedback and a quick debugging cycle.

When you fixed all the shorts and want to start running sign-off, you simply

omit the "-recon -si" command line options. When you are LVS-clean, you can

then proceed with other downstream tasks like running parasitic extraction

(Star-RC, QRC, Calibre xACT, or Ansys Totem), or reliability verification

(Calibre PERC), etc.

In summary, none of the steps leading up to standard Calibre LVS has changed,

none of the downstream flow has changed, it's that iteration time in the

middle that's been shrunk.

WHAT ABOUT CADENCE & SYNOPSYS DRC/LVS TOOLS?

I've not heard of Cadence doing anything in this area, as Anirudh is still

trying to get Pegasus off the ground and can't spend cycles on these plus-1

features like thisyet.

As for Synopsys, Aart has something called ICV Explorer DRC.

Here is their data sheet.

My spy says he hasn't seen it in use anywhere. He said:

"If Synopsys spent as much time in development as they did

wordsmithing their datasheet, Aart would own this niche.

Supposedly it is free with the ICV license. But you get

what you pay for. And there is no LVS version."

TAKEAWAY

Fixing shorts may not sound like a big deal overall, but for LVS debug, 80%

of the time is spent chasing and fixing shorts. Any way to cut that cycle

time is a win for your team's overall schedule.

If Sawicki's Calibre minions have a quickie LVS/DRC linter that's 10x to

30x faster than standard Calibre runs, why not give it a look see?

- John Cooley of DeepChip.com

---- ---- ---- ---- ---- ---- ----

Related Articles

A cheeky Sawicki invites Anirudh to Calibre 4,140 cloud CPUs lunch

Joe Sawicki smirks at Cadence Pegasus' 3 big critical DRC failings

Calibre scales 2,048 CPUs 16nm 700mm2 full chip DRC in 3.5 hours

Juan Rey -- The Most Interesting Man in EDA about the Future of DRC

Anirudh's 19 jabs at Joe Sawicki's Calibre with his Pegasus launch

Join

Index

Next->Item

|

|