#### **A Deterministic Flow** Combining Virtual Platforms, Emulation, and Hardware Prototypes

Presented at Design Automation Conference (DAC) San Francisco, CA, June 4, 2012. Presented by Chuck Cruse

## **FPGA Hardware Prototypes Provide**

- §"Real World" exercise of the System

- Closest to Chip Behavior

- Interacts with other Physical Devices in Real-Time

§Hardware/Software integration vehicle

Setection and debug of subtle system-level "Real Time" problems (Clock Domain Issues)

Specification verification amongst various compatible products (Plugfest)

### Sustomer demo

# **Overcoming Issues for the FPGA Hardware Prototype**

Solution Must hit a narrow window of opportunity

- Delays in the development of the prototype reduce effectiveness

- Svisibility of internal signals, while improving, remains a challenge

- SQuick turnaround of incremental changes improving, but could be better

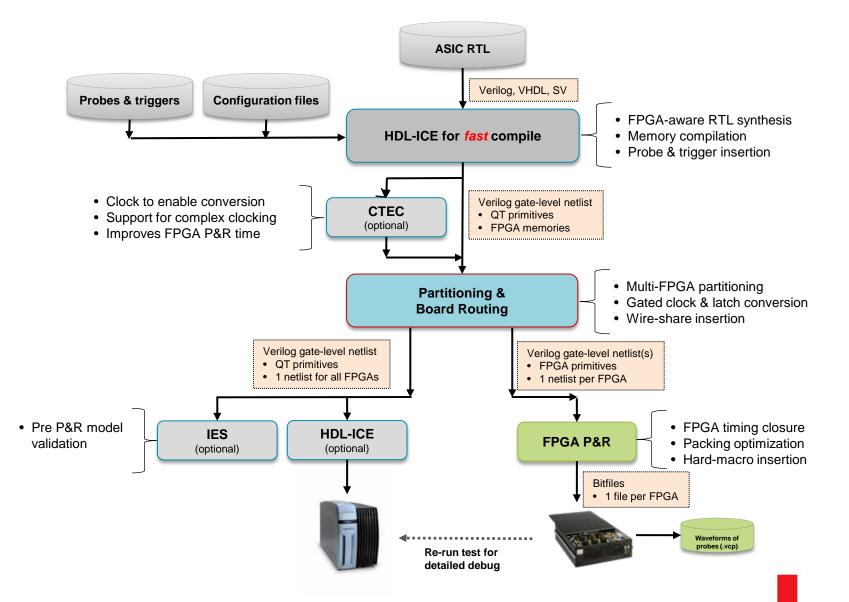

### Multi-FPGA Prototyping Flow Example: Cadence Rapid Prototyping Platform

#### cādence°

# **Code Staging and Cross Communication**

# **Moving Up the Food-Chain**

- In the past, FPGA-specific RTL has been simulated in order to demonstrate basic functionality before downloading bitstreams into the lab.

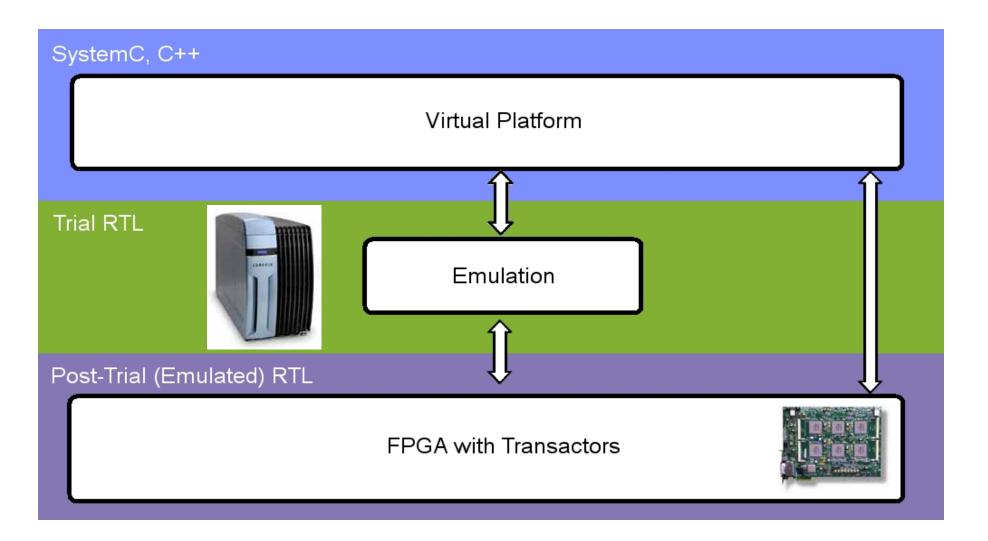

- §For the future, the hope is that this approach could be expanded to include Virtual Platforms and Emulation

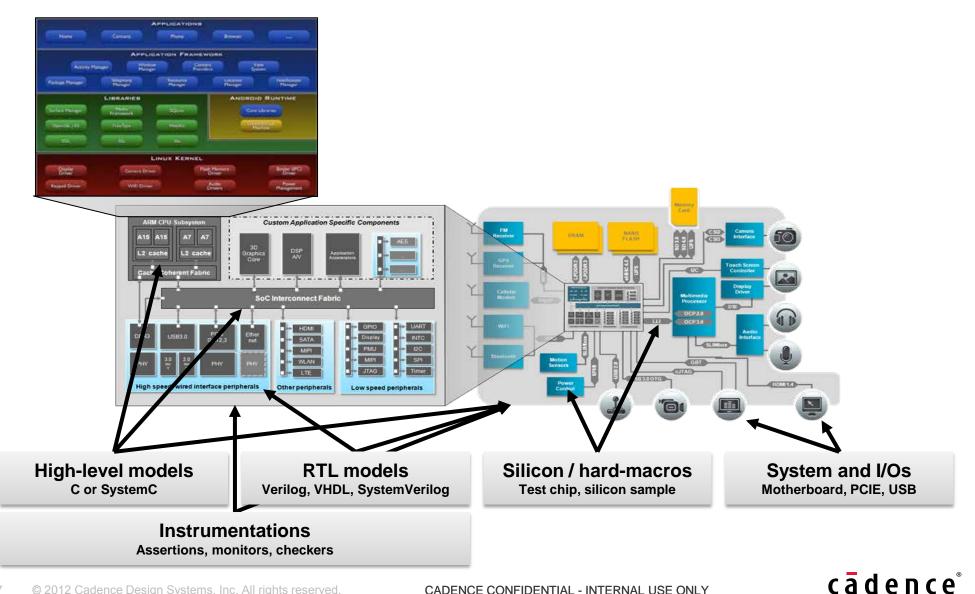

### Complex Projects Require Many Model Types

Need for optimized reuse of existing IP assets

## **Virtual Platforms for Emulation and FPGA**

**§**System-Level Virtual Platform Modeling

- Early HW/SW Integration

- Pre-RTL mutual reinforcement of HW & SW

- Reduce "Big-Bang" Integration Surprises

- Architectural Benefits

- "What-If" scenarios can be tried at high level

- Bring .pdf "to life" Reduce EDS/RTL Mismatches

## **Virtual Platform Goals**

- **§** *Deterministic* Approach Avoid "surprises" in integration/development

- **§** Leverage Virtual Platform and Emulation to create FPGA Hardware Prototype

- **§** Retain the benefits of software simulation

- Cycle-accuracy may suffer, but emulation and the hardware prototype will catch these issues

- § Begin hardware/software integration very early in the development process

- Section Section Should be more transparent when "crossing over" from the virtual world to the hardware prototype

- Emulation/HW Prototypes always result in a "step function" effort

- "Step function" problem should be reduced when the virtual platform is incorporated into the flow

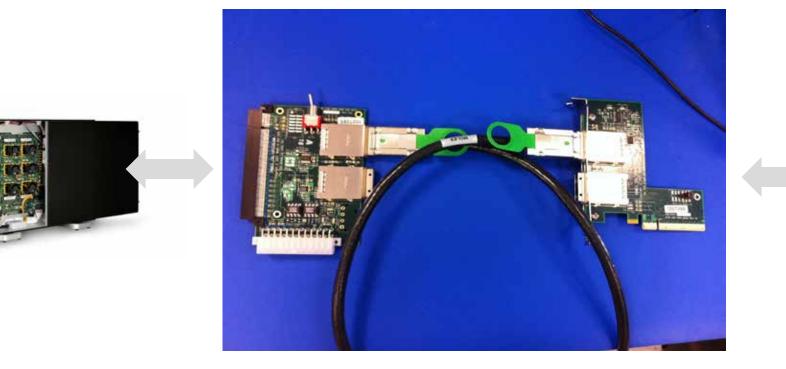

# SCE-MI Open Standard for Virtual Platform and FPGA

- Several Serial Protocols could be expected to serve as a vehicle for SCE-MI transactions

- PCle

- Altera SerialLite II

- Xilinx Aurora

- SAS/SATA

- **§** OSCI and Accellera Merge

- OSCI chair Eric Lish and Accellera chair Shishpal Rawat sign merger documents to create Accellera Systems Initiative\*

- This validates a SCE-MI and SystemC approach to FPGA and Virtual Platform development with a rich and developing set of open standards

- \* http://www.accellera.org/about

### PCIe Interface Kit Flexible, scalable 1 – 4 lanes

### **Evolving System Development And Verification**

#### CLOSED

- Single-vendor point solutions

- Proprietary

#### FRAGMENTED

- Niche offerings

- Unconnected

#### LIMITED

- Single level of abstraction

- Block-to-system migration issues

#### OPEN

- Compatible with standard SW debuggers

- Support for standard interfaces

#### CONNECTED

- Multi platform compile compatibility

- SpeedBridge Adapters

#### SCALABLE

Multiple hardware configurations

Now

Easy transition from emulation

Then

cādence<sup>°</sup>

## **End-Of-Day Benefits**

§Reduced spins of the design

§Much faster chip-evaluation when silicon arrives

- Software ready to go

- Integration/System-Engineering team already up to speed on the device

Seffective widening of the pre-silicon testing window

Storage. Networking. Accelerated.<sup>™</sup>